一、 概述

二、基本概念

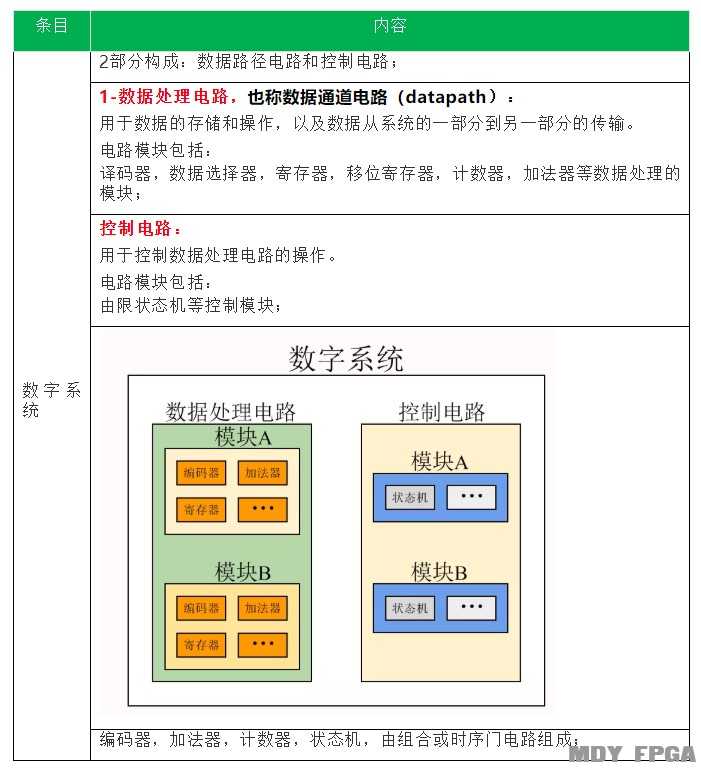

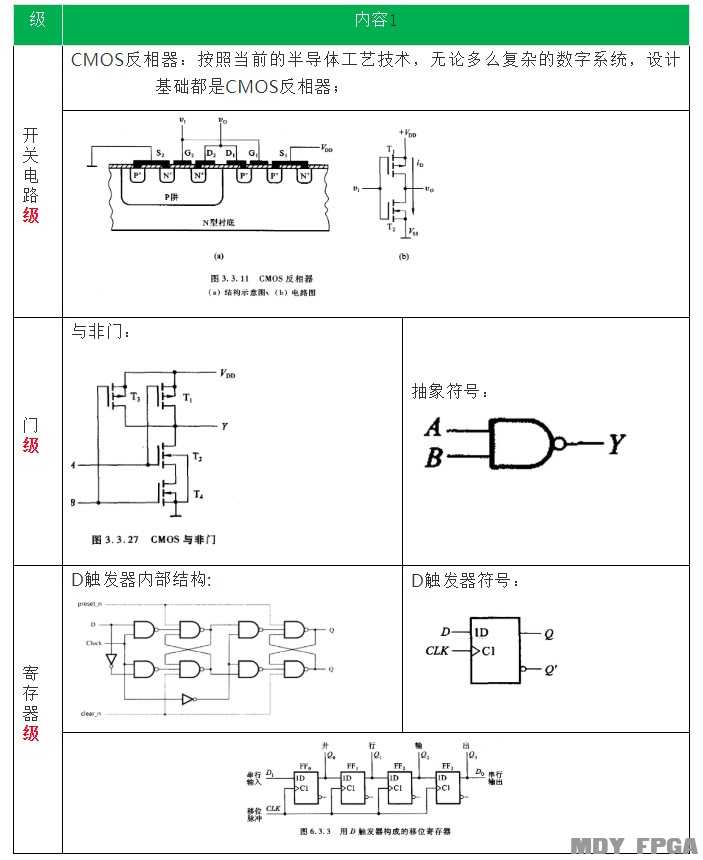

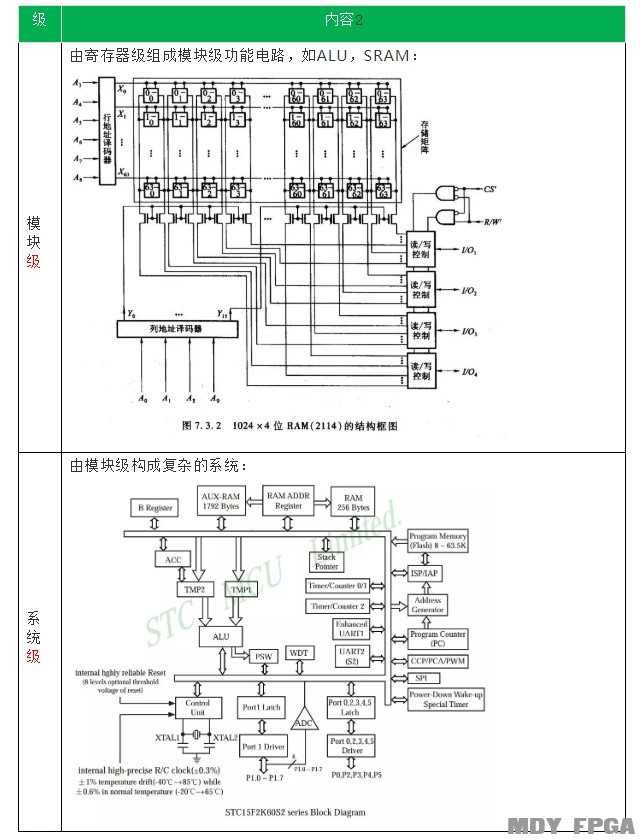

2.2硬件電路

2.2 數(shù)制

2.2.1 進(jìn)制轉(zhuǎn)換表

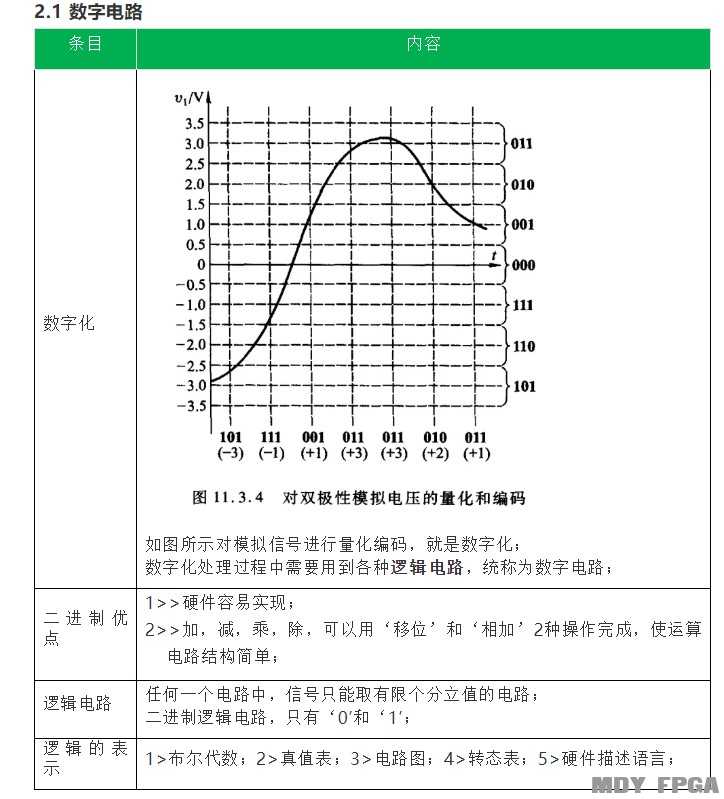

2.3 編碼

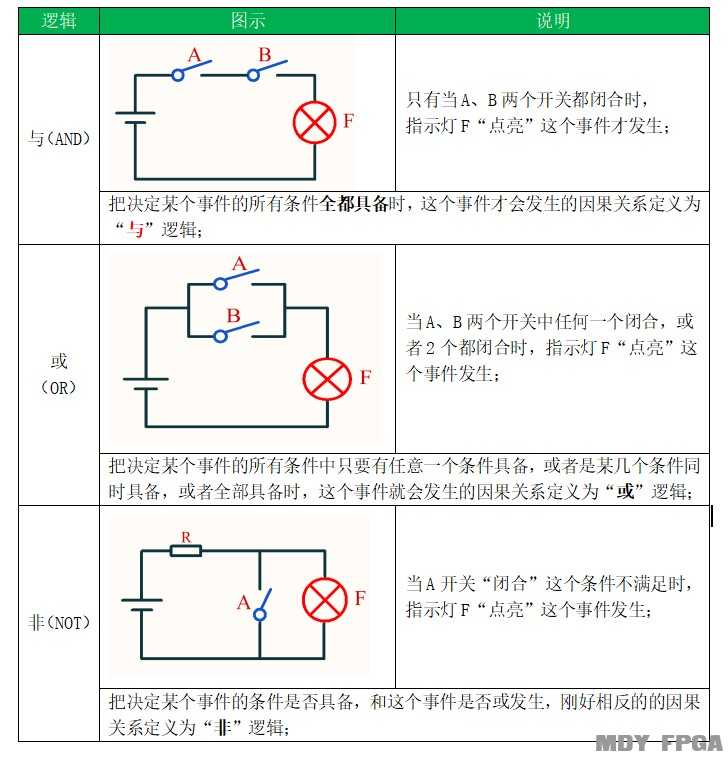

2.4 邏輯代數(shù)基礎(chǔ)

2.4.1 布爾代數(shù)

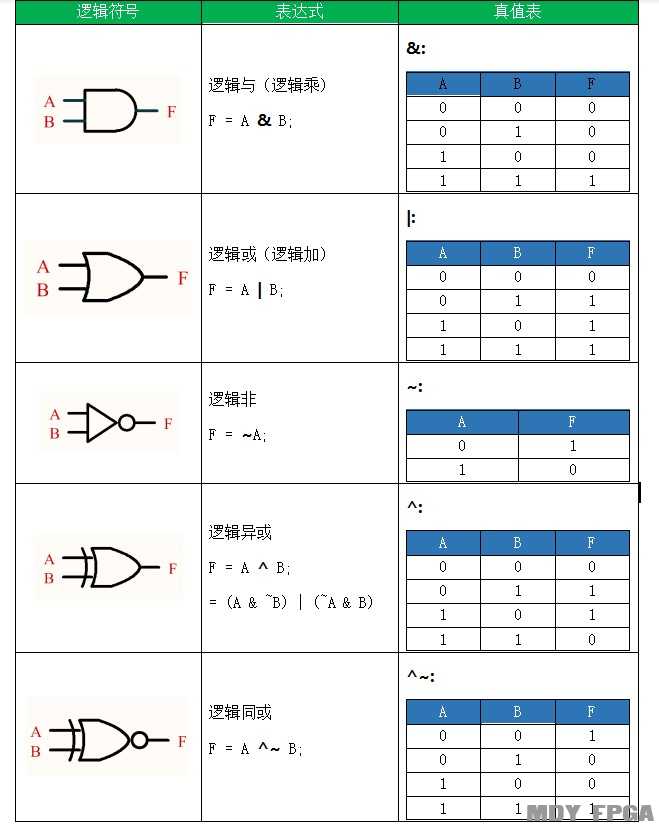

2.4.2 基本邏輯運(yùn)算

2.4.3 基本邏輯表達(dá)

2.4.4 邏輯函數(shù)

2.5 電路分類

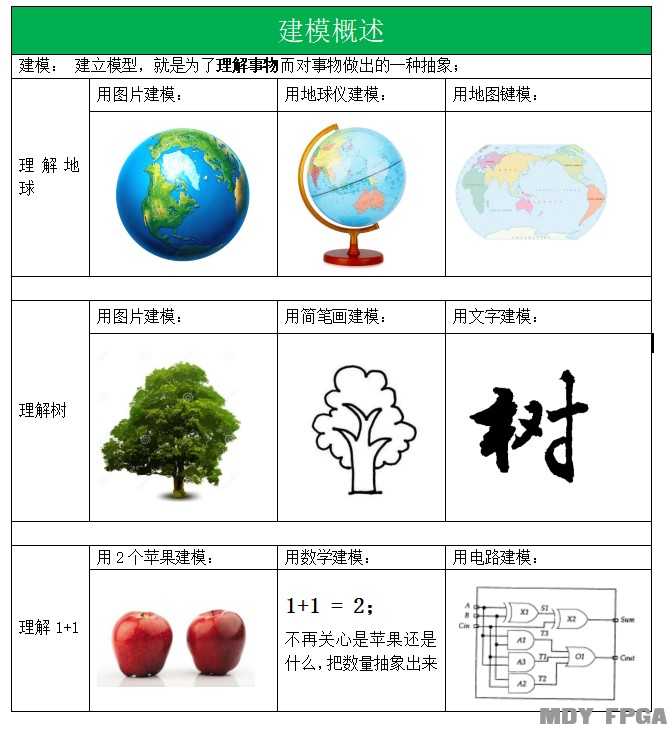

2.6 建模

2.6.1 建模概述

2.6.2 Verilog邏輯設(shè)計(jì)

三、 組合邏輯電路

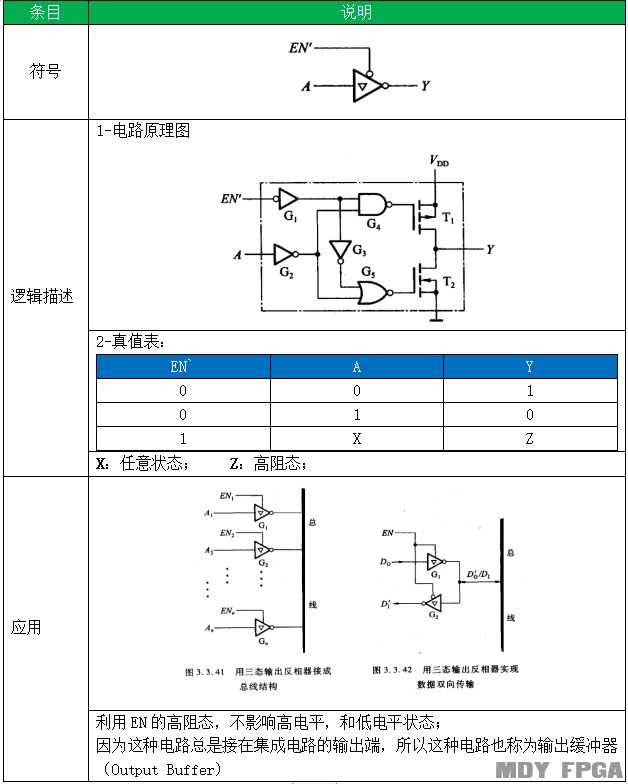

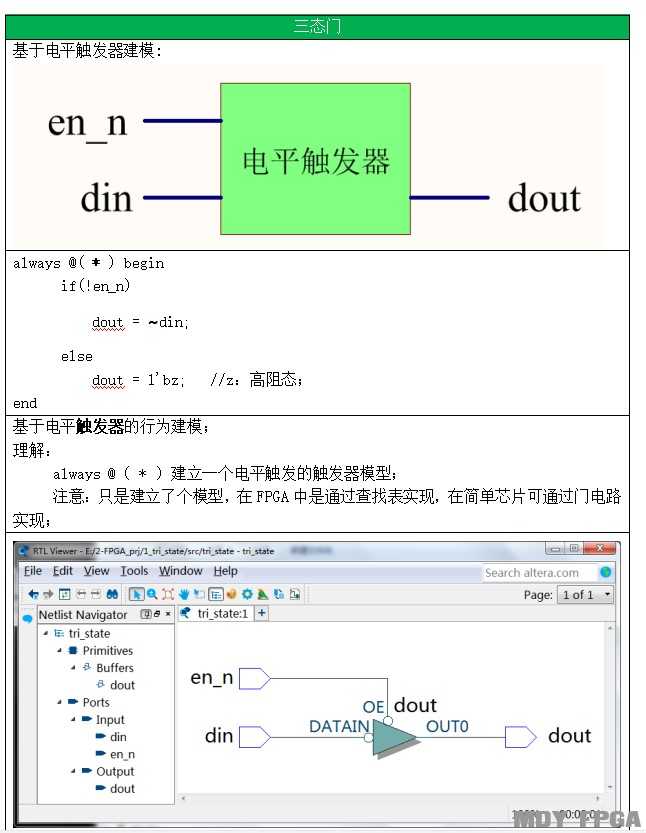

3.1 三態(tài)門3.1.1 工作原理

3.1.2 行為建模

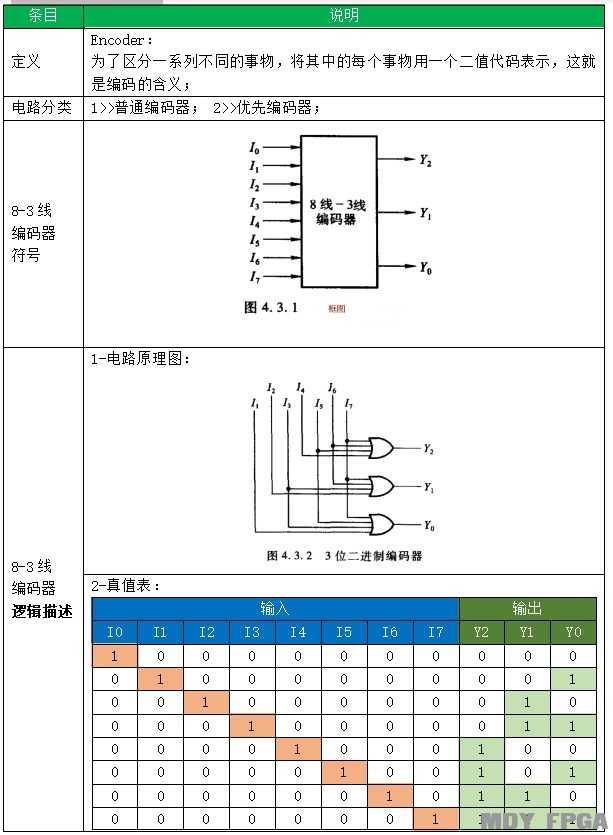

3.2 編碼器

3.2.1 工作原理

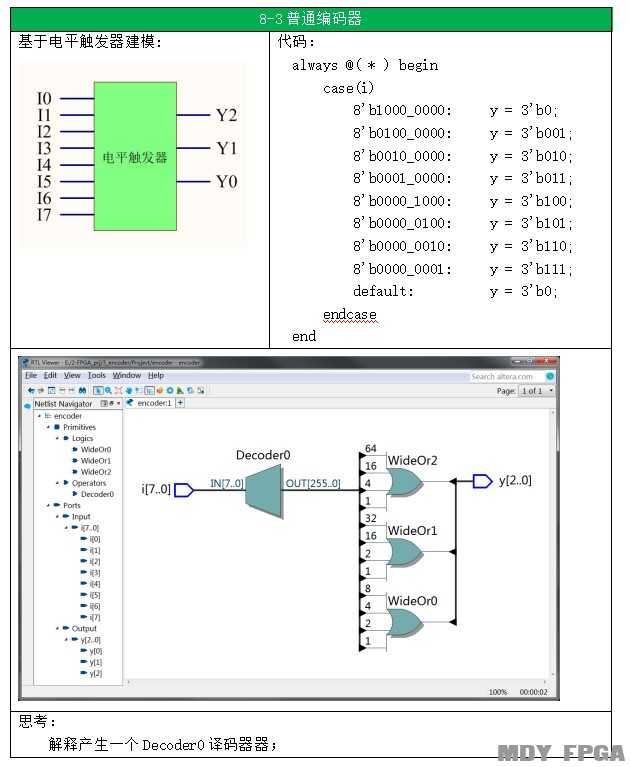

3.2.2 行為建模

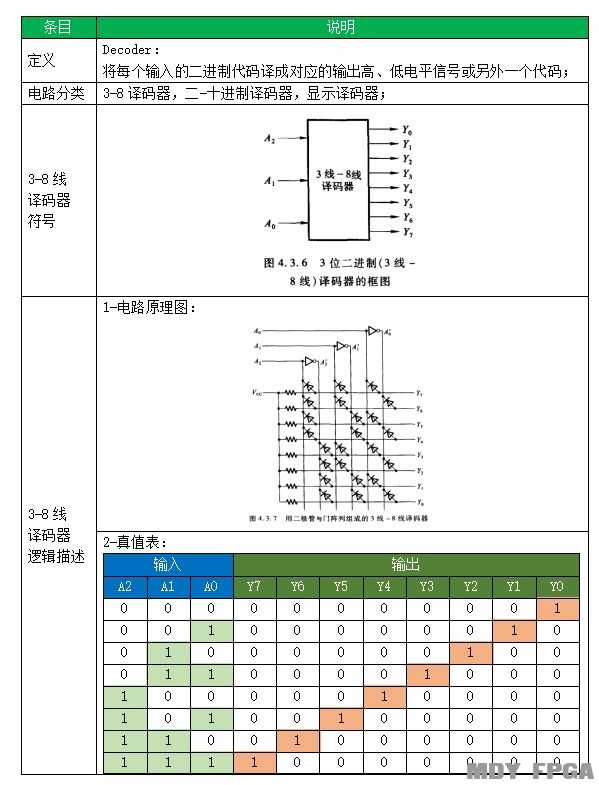

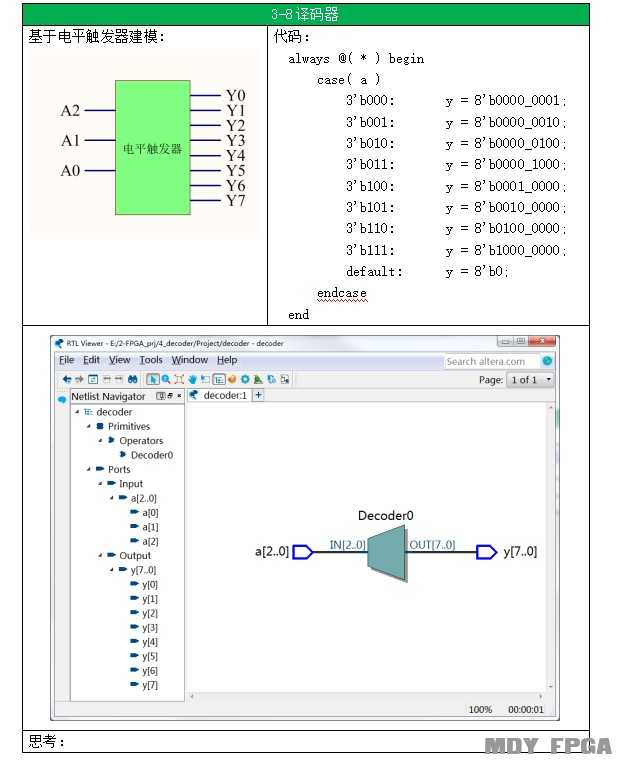

3.3 譯碼器

3.3.1 工作原理

3.2.2 行為建模

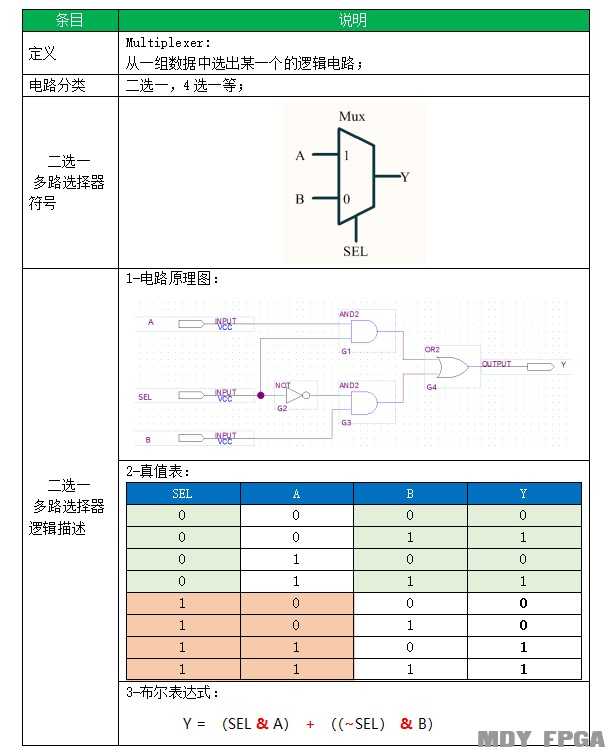

3.4 數(shù)據(jù)選擇器

3.4.1 工作原理

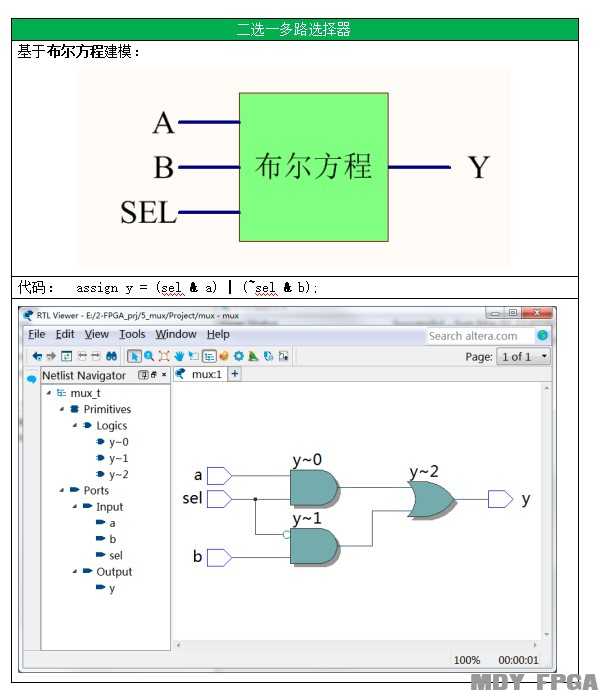

3.4.2 行為建模1

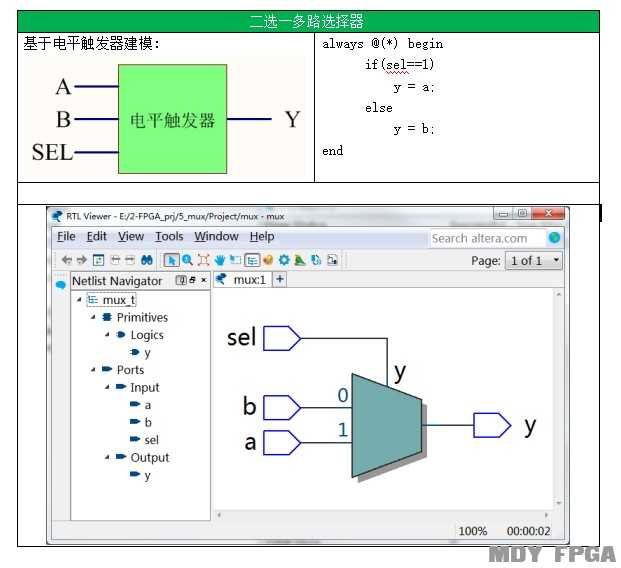

3.4.3 行為建模2

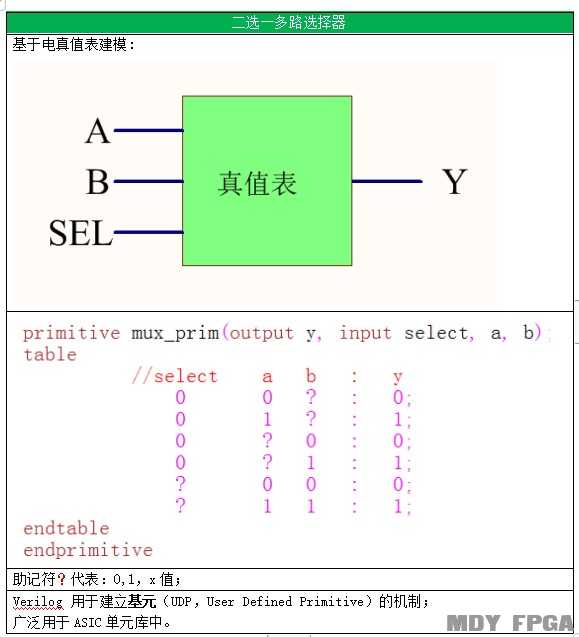

3.4.3 真值表建模

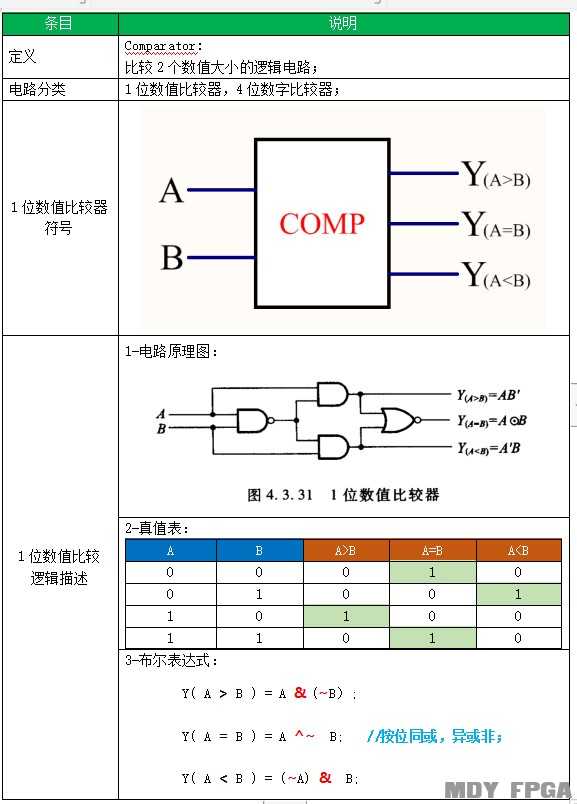

3.5.1 工作原理

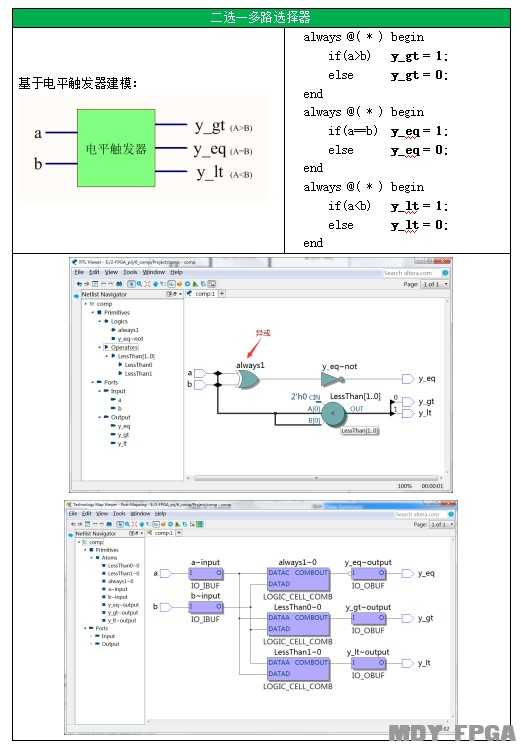

3.5.2 行為建模1

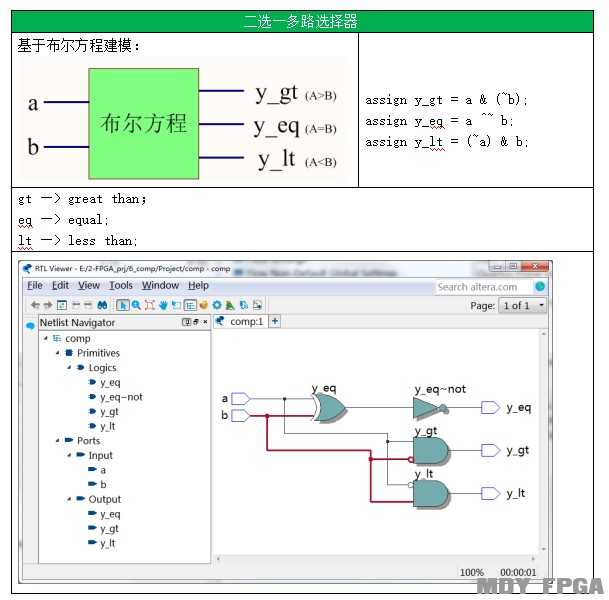

3.5.2 行為建模2

四、 時(shí)序邏輯電路

4.1 概述

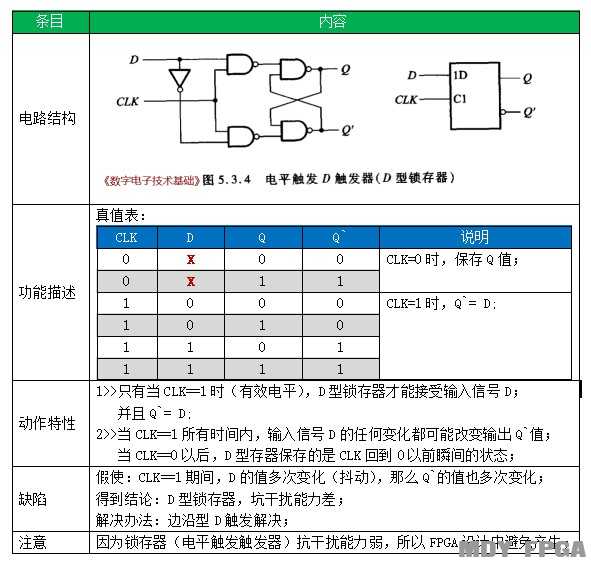

4.2 D型鎖存器

4.2 D型鎖存器

4.2.1 工作原理

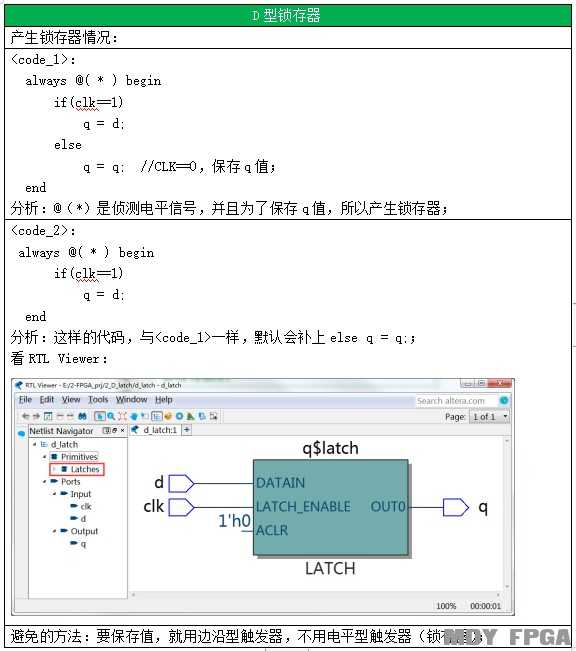

4.2.2 行為建模

4.2.3 避免鎖存器

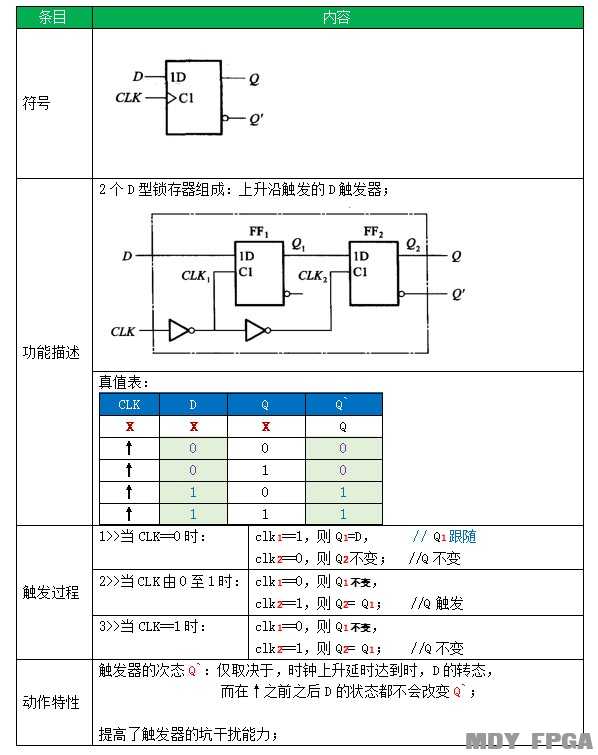

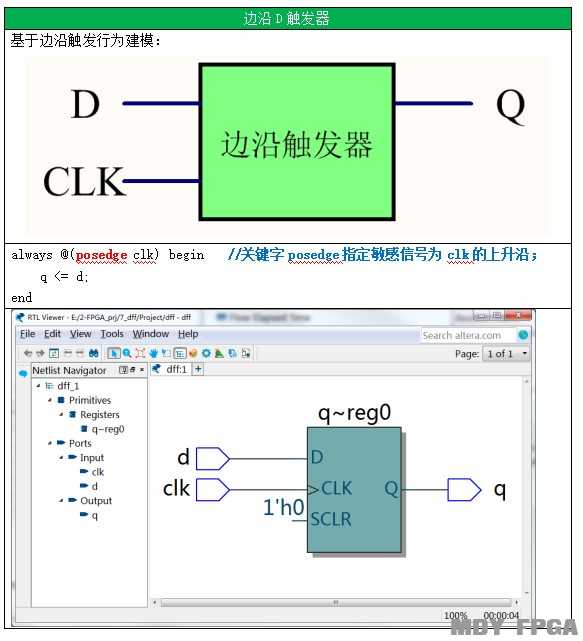

4.3.1 工作原理

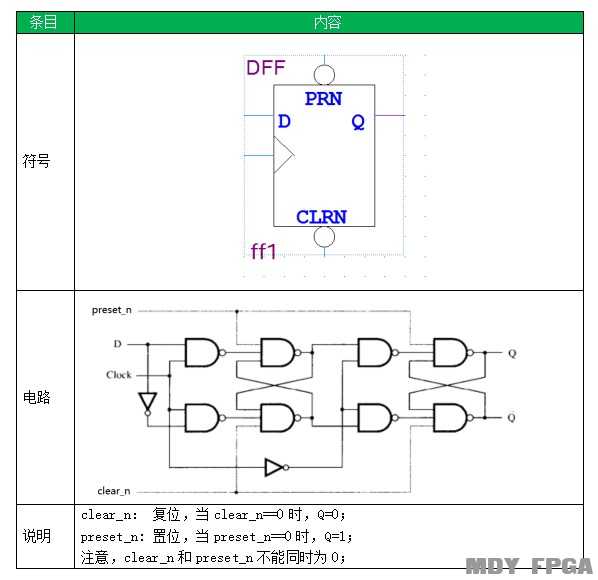

4.3.2 復(fù)位/置位D型觸器

4.3.3 行為建模

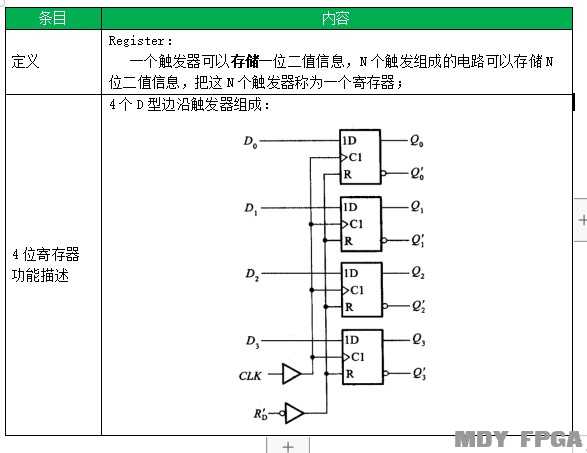

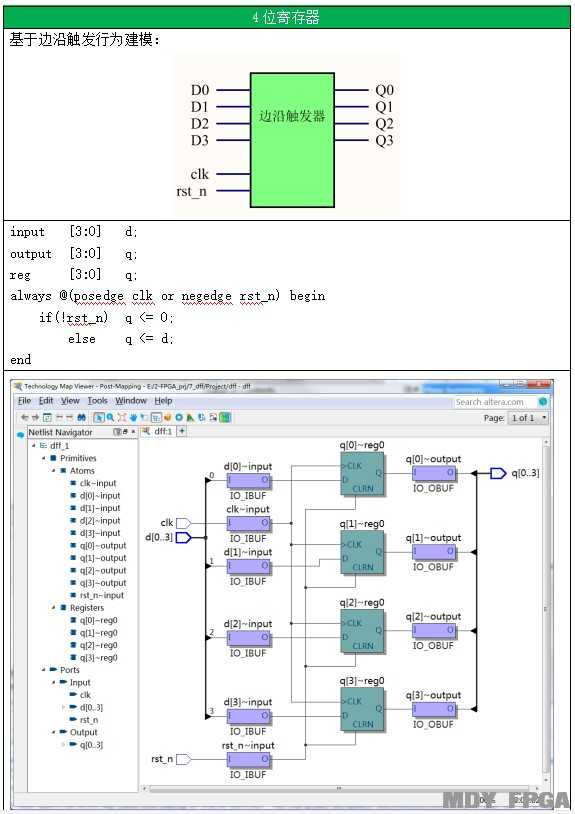

4.4 寄存器

4.4.1 工作原理

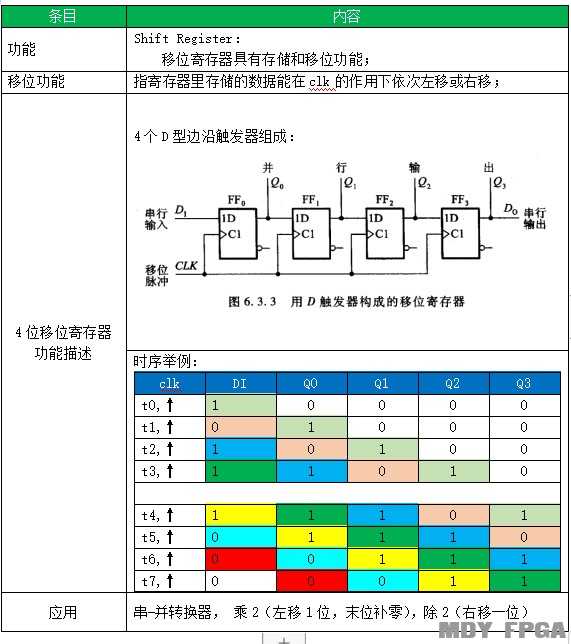

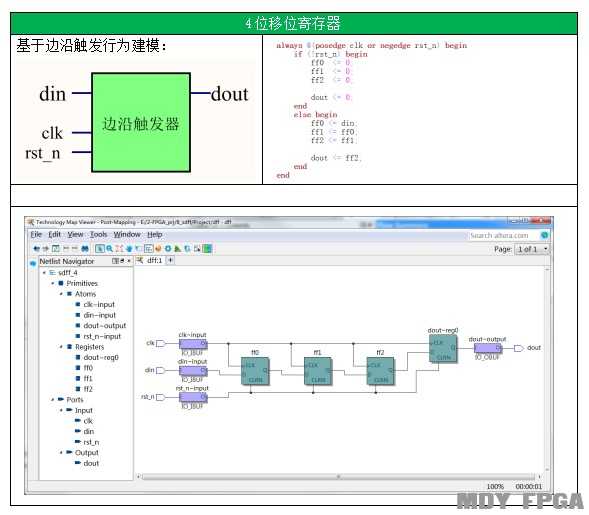

4.5 移位寄存器

4.5.1 工作原理

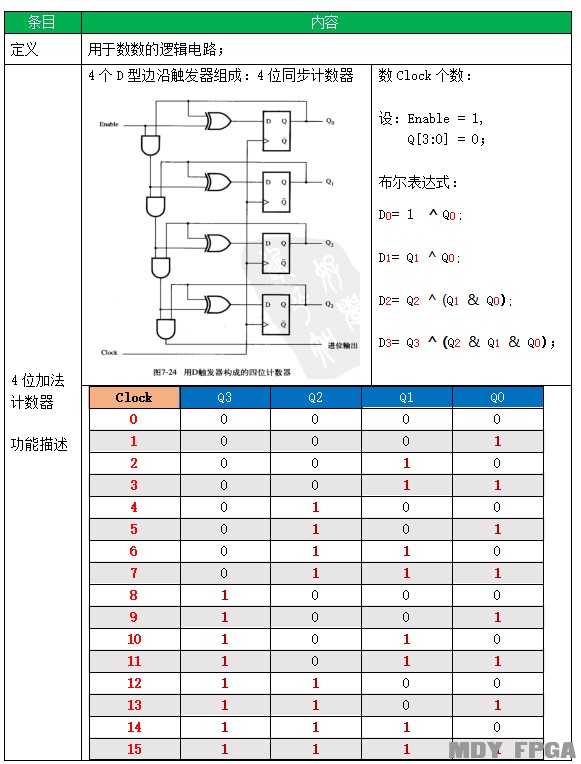

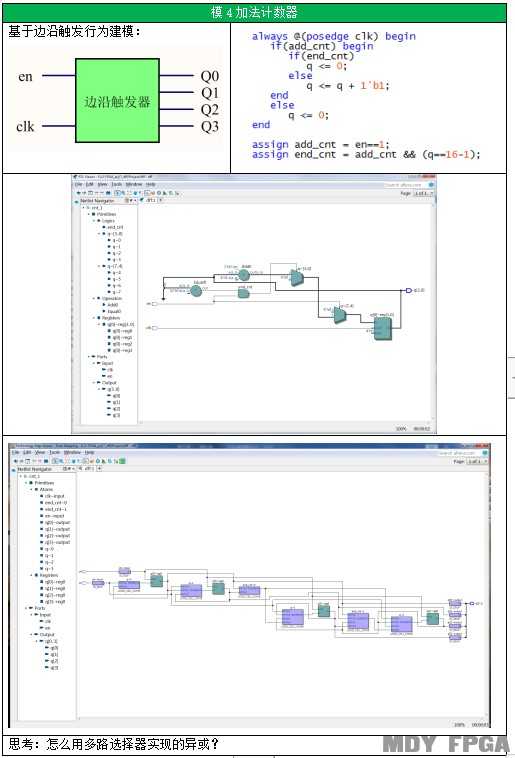

4.6 計(jì)數(shù)器

4.6.1 工作原理

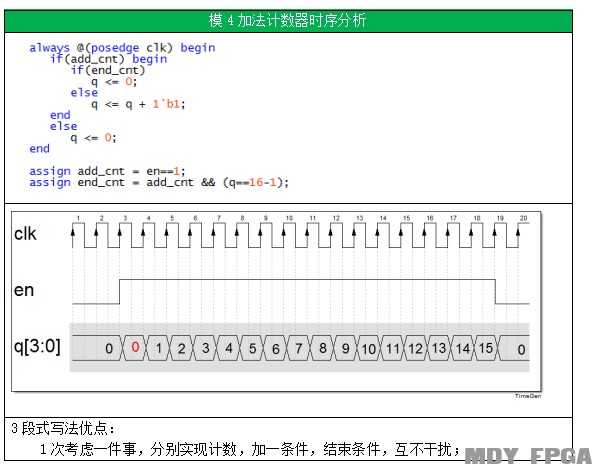

4.6.2 行為建模

4.6.3 時(shí)序分析

4.7 狀態(tài)機(jī)

4.6.1 概述

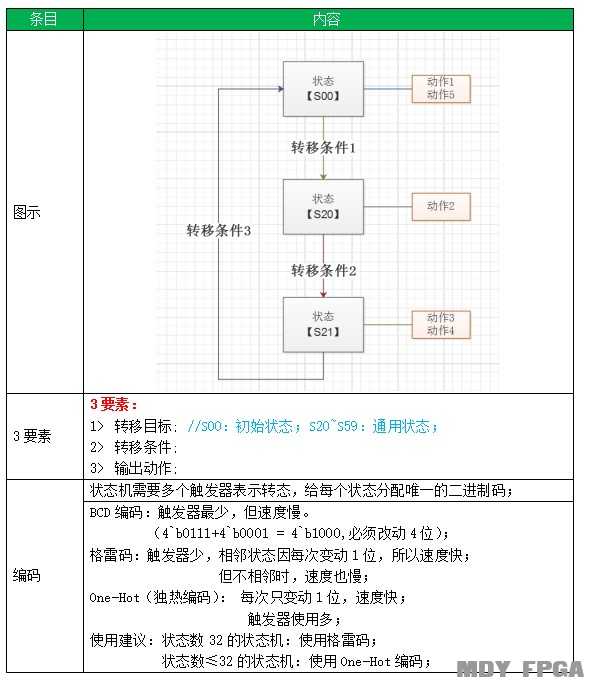

4.6.2 SFC

4.6.3 狀態(tài)機(jī)描述

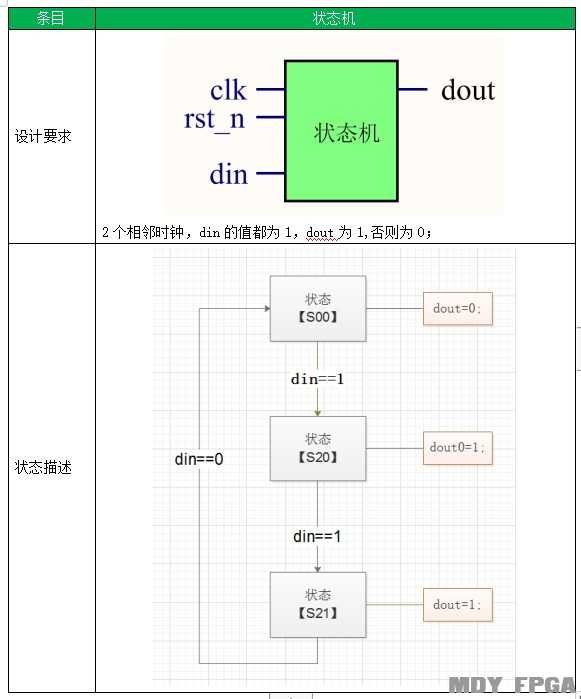

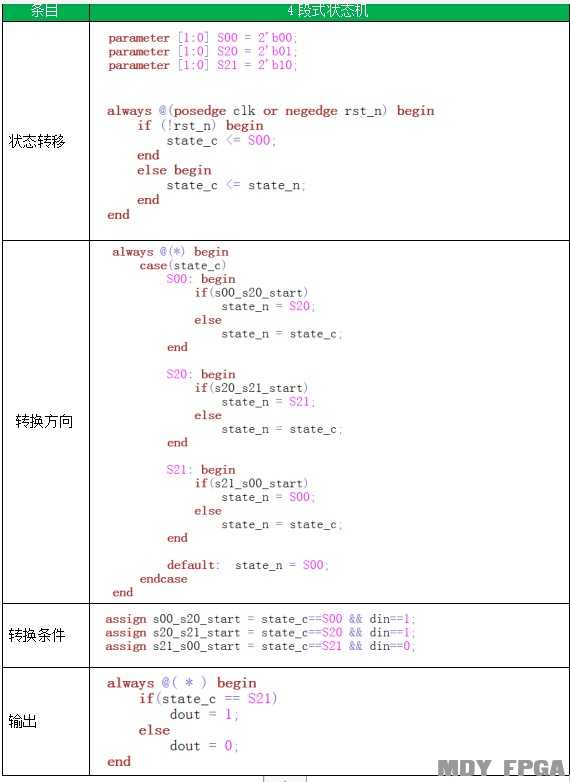

4.6.4 狀態(tài)機(jī)實(shí)現(xiàn)

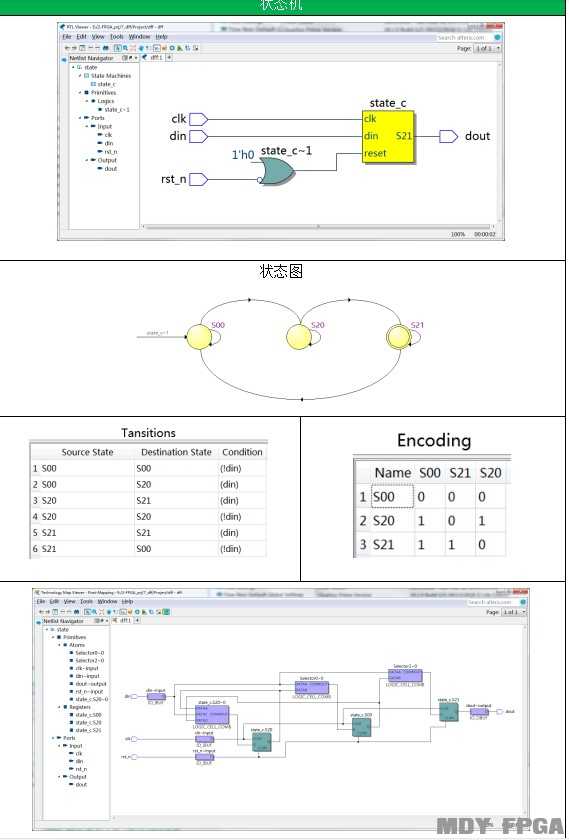

4.6.5 狀態(tài)機(jī)圖示

五、 算術(shù)運(yùn)算電路

5.1 加法器

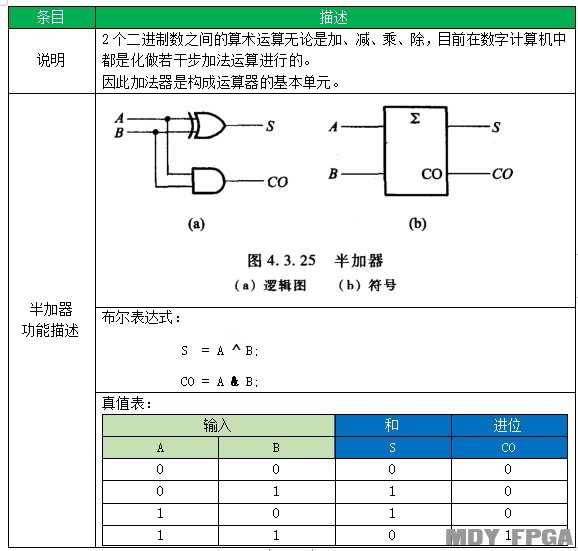

5.1.1 半加器工作原理

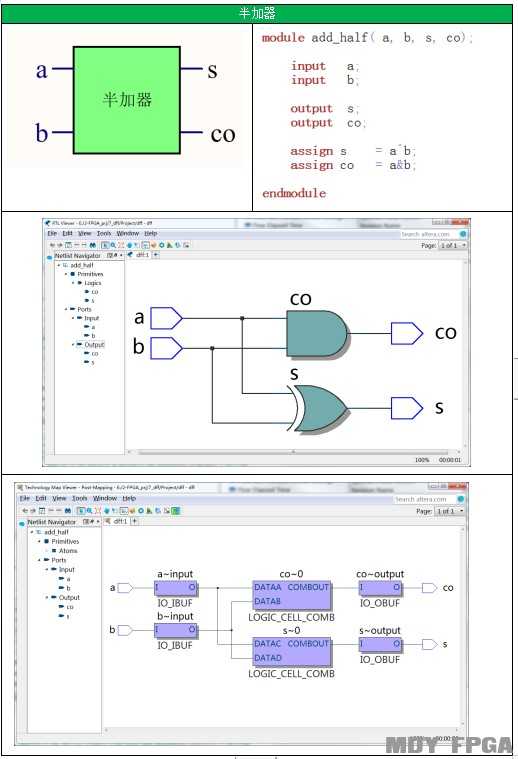

5.1.2 半加器行為建模

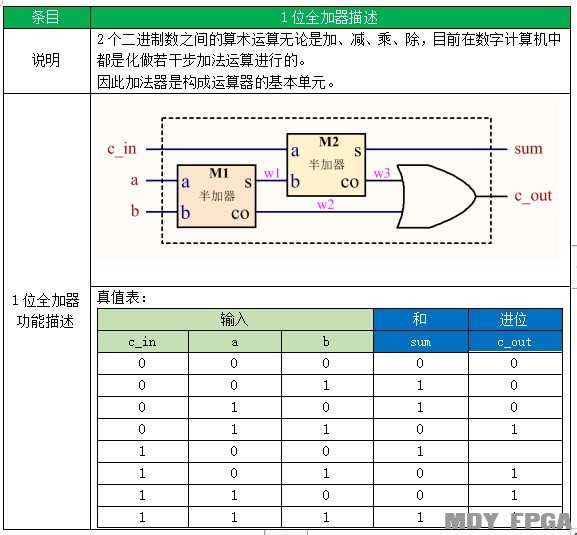

5.1.3 1位全加器工作原理

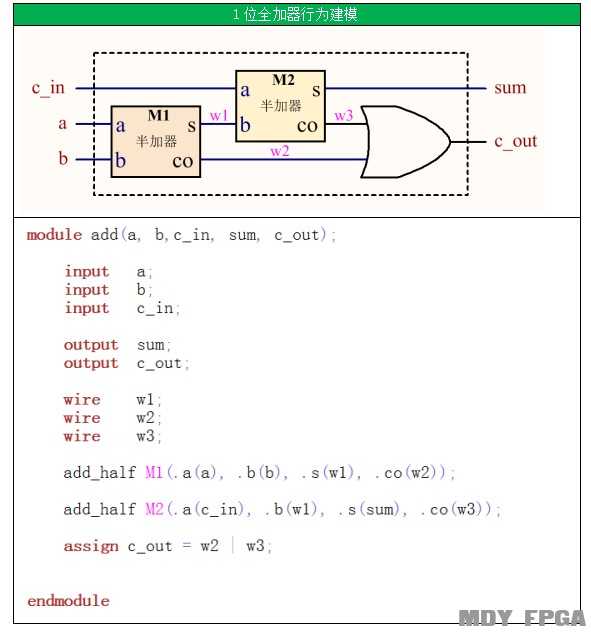

5.1.5 1位全加器行為建模

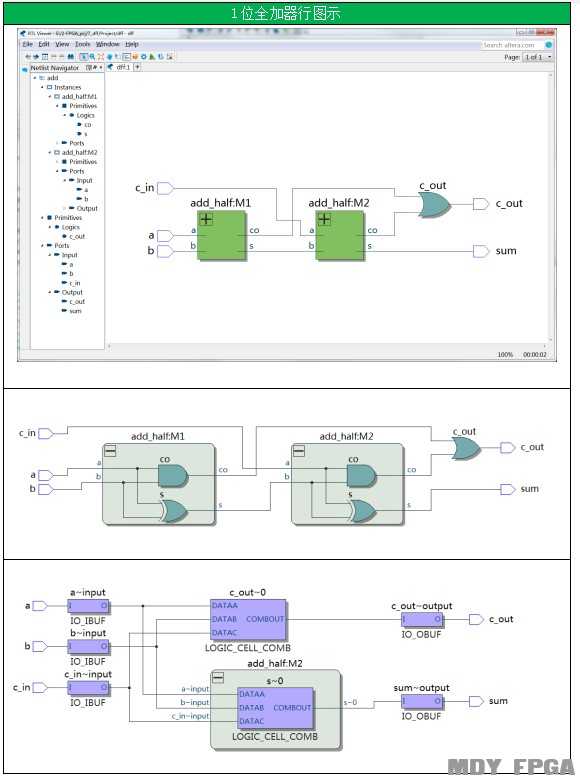

5.1.6 1位全加器行圖示

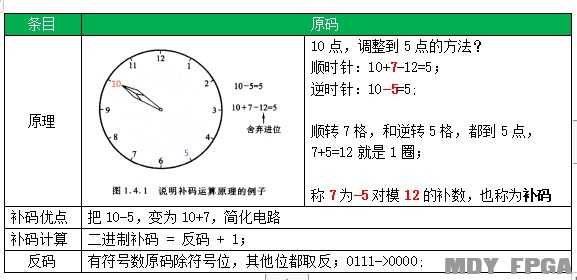

5.2 減法器5.2.1 原碼

5.2.1 補(bǔ)碼

5.2.1 補(bǔ)碼

溫馨提示:明德?lián)P2023推出了全新課程——邏輯設(shè)計(jì)基本功修煉課,降低學(xué)習(xí)FPGA門檻的同時(shí),增加了學(xué)習(xí)的趣味性,并組織了考試贏積分活動(dòng)

http://www.cqqtmy.cn/ffkc/415.html

(點(diǎn)擊→了解課程詳情?)感興趣請(qǐng)聯(lián)系易老師:13112063618(微信同步)

明德?lián)P除了培訓(xùn)學(xué)習(xí)還有項(xiàng)目承接業(yè)務(wù),擅長(zhǎng)的項(xiàng)目主要包括的方向有以下幾個(gè)方面:

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(IMX472 IMX492)

3. PCIE采集系統(tǒng)

4. 圖像項(xiàng)目

5. 高速多通道ADDA系統(tǒng)

6. 基于FPGA板卡研發(fā)

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關(guān)信息可以聯(lián)系:易老師13112063618(微信同號(hào))

本文TAG:

上一篇:沒有了!下一篇:【教程】史上最干貨的Verilog語法課程_6小時(shí)掌握Verilog語法