一、項目背景

明德揚(MDY)為中科院某所研制一款X射線采集和處理設備,該設備采用了AD8488和AD9244兩款芯片進行X射線的采集,采用FPGA進行處理,并通過千兆網口上送至上位機處理。

二、硬件原理

高能射線轟擊碲鋅鎘晶體后,在晶體內形成空穴,在晶體上施加一個高壓電場,使電子快速轉移。AD8488接收到傳感器輸出的電荷,經過芯片內部轉換、放大,被高速ADC采集。轉換后的數據經過對齊、組幀,通過千兆網傳輸至上位機。最后由Matlab將接收到的數據轉換為能譜圖像。項目整體框圖如圖1所示:

2.1碲鋅鎘(CZT)探測器碲鋅鎘晶體

是一種性能優良的核輻射探測器材料,對X、γ射線有很高的探測效率和很好的能量分辨率,而且可以在室溫下工作。對于碲鋅鎘核輻射探測器。當X、γ射線等高能粒子射線打入探測器的介質晶體時,射線粒子會與介質晶體中的原子產生能量交換,使射線很快損失掉一部分能量,這部分能量被晶體中的原子所吸收,促使其電子從滿帶躍遷到導帶上,從而在導帶產生電子,在滿帶剩余空穴,這便形成了可以用來形成電信號的電子-空穴對。在介質晶體的兩端電極上加一高壓外加電場,在高壓電場作用下介質晶體內部的電子-空穴對分別向兩端電極漂移,電信號通過電極被收集起來,在兩端電極上形成微弱的感應電流。當前,碲鋅鎘探測器兩個重要發展方向是:多塊大體積并行探測器和面元陣列探測器。前者由多塊體積大于1cm的碲鋅鎘晶體陣列組成,這類探測器解決了單個探測器體積小,總探測效率低的缺點,大大縮短了測量時間,尤其適于便攜式譜儀系統,可應用于環境、港口、鐵路貨物等的放射性監測。后者是由碲鋅鎘晶體面元陣列組成,主要應用于核醫學、天體物理等領域的能譜成像。本項目采用的是碲鋅鎘晶體面元陣列作為前端傳感器。

2.2電荷積分放大器原理

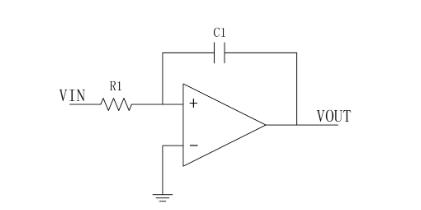

圖1為運放積分放大器的電路圖

圖1理想積分放大器電路圖

根據運放虛短可知,反向端與同相端電壓相等,又由虛斷可知,通過R1的電流與通過C1的電流相等。通過R1的電流為:

由此可得,運放的輸出電壓等于對輸入電壓在時間上的積分。若輸入端為電荷采集裝置的話,那么運放的輸出與輸入端的電荷量成正比。兩部分組合起來就是電荷積分放大器。

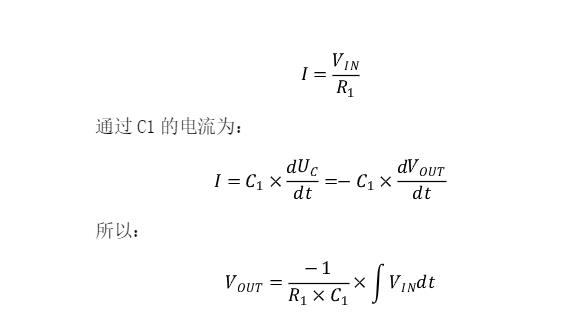

2.3AD8488簡介

AD8488是一款128通道模擬前端,為高性能數字X射線系統而設計。它的模擬通道由一個積分器和增益可選的單端轉低阻抗差分輸出組成。該模擬通道將X射線或光電二極管檢波器收集的電荷轉換成電壓信號。通道由CMOS晶體管組成,這些晶體管采用典型高輸入阻抗的CMOS門。該設備的積分器采用一系列可選電容值,產生與電荷有關的電壓,可適應廣泛的輸入電荷值。單端輸入轉差分輸出電壓放大器位于積分器之后,在這里偏移和低頻噪聲電壓從輸入電壓中減去。一條128:1通道差分MUX位于緩沖器之后,驅動模擬輸出緩沖。同時還提供開關驅動器和某些數字計時功能;這些功能全部集成在255引腳BGA基板上。全部128通道的電荷轉換是同步進行的,之后便采用7位地址編碼生成順序電壓輸出讀數。一共兩次序列,對全部128通道進行采樣。邏輯控制輸入CS_A和CS_B分別選擇通道地址的下限和上限64模塊。

2.4AD8488工作原理

AD8488電路結構如圖2所示:

圖2AD8488電路結構圖

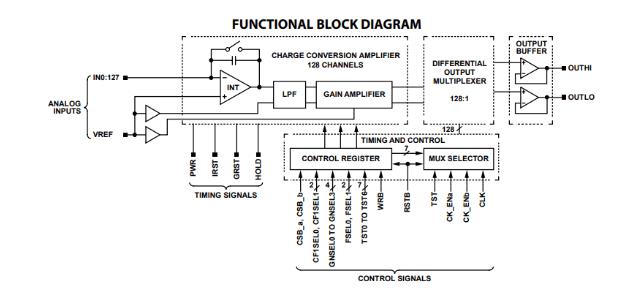

如圖所示,AD8488主要由四部分構成。分別為前置電荷量轉換器、差分輸出選擇器、輸出緩沖器和時序/控制部分。前置電荷量轉換器為128通道電荷積分放大器,每一個通道由一個放大器,一個低通濾波器和一個二級放大器構成。電路結構圖如圖3所示:

圖3電荷量轉換器結構圖

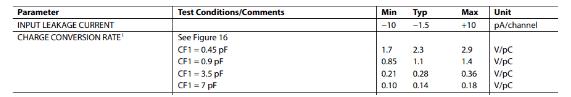

前端采集到的電荷信號通過第一級積分放大器進行轉換,共有四檔可選。各檔位轉換參數如圖4所示:

圖4電荷積分放大器轉換參數

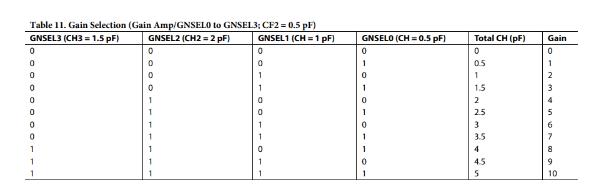

這四檔分別由四種不同容值的反饋電容(CF1)控制。當CF1=0.45pF時,輸出典型值為2.3V/pC(單位為伏特每皮庫倫,指每積分1皮庫倫,輸出為1V。1pC=C);當CF1=1.1pF時,輸出典型值為1.1V/pC,以此類推。CF1容值越大,增益越低。第二級低通濾波器實際上是一個保持裝置,由一個電阻R1和一個電容構成。第一級放大器輸出的電壓信號通過R1給電容充電,以便于第二級放大器對進行積分放大。因此相當于一個低通濾波器。的參數由GNSEL[3..0]選擇,參數如圖5所示:

圖5參數選擇表

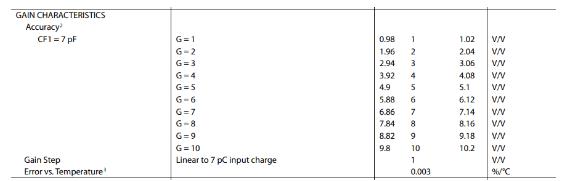

注:GNSEL[3..0]寄存器只能選擇的容值,并不代表增益。上圖中所表示的增益實際上是當二級放大器的反饋電容為0.5pF是,不同的容值下對應的增益。第三級放大器與第一級相同,也是一個電荷積分放大器。只不過第一級輸出的電壓信號是對芯片輸入的電荷量的積分,然后該電壓信號對第二級的電容進行充電,之后通過第二級放大器對的電荷量積分,最終輸出新的電壓信號,形成二次放大的效果。第二級積分放大器增益由CF2控制,共有10檔,增益單位為V/V。注:因為第一級放大器已經將電荷信號轉換為電壓信號,因此第二級放大器的電壓為伏特每伏特。增益表如圖6所示:

圖6第二級積分放大器增益表

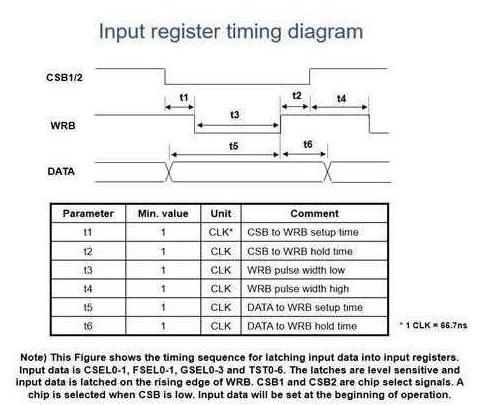

2.5AD8488的控制時序

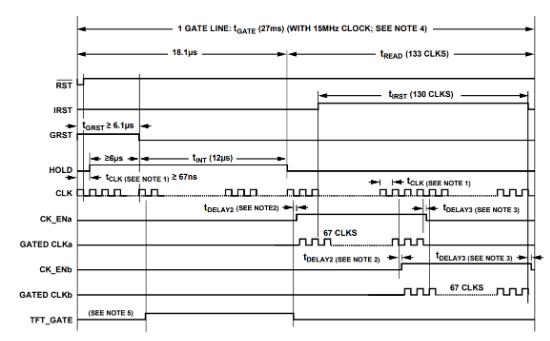

圖7AD8488控制時序圖

AD8488的控制時序如圖7所示。主要控制信號如下:

SWIRST是指IRST,用于控制第一級積分器的開關

GNSEL0~3,用于控制中間部分的開關,0~3是并行的關系

SWHOLD是指HOLD信號,用于控制通路

SWGRST是指GRST信號,用于控制增益放大器的部分。

采集開始前,全局信號復位,RST信號拉低半個CLK。GRST信號拉高至少6.1us,旁路第二級放大,6.1us后拉低。HOLD信號在積分時拉高18.1us,18.1us后,也就是進行通道選通的時候拉低,斷開前端積分放大電路,防止影響后端采樣。后端數據選通總共占133個CLK,由CK_EN信號控制前/后64通道,由GATED_CLK來控制各64通道的輸出。其中CK_EN還控制著前/后64通道的控制寄存器,具體控制時序如圖8所示:

圖8AD8488控制寄存器時序

2.6信號采集

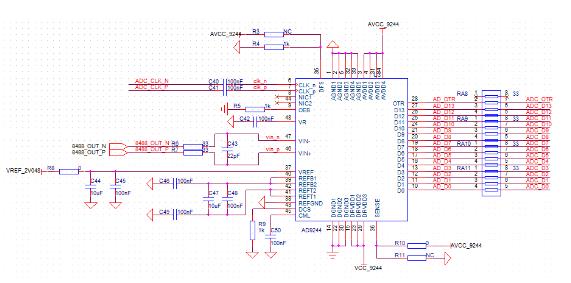

信號采集部分使用了AD9244模數轉換器,該芯片是一款65MSPS,14bit的ADC芯片。AD9244電路原理圖如圖9所示:

圖9AD9244原理圖

信號輸入采用直流耦合的方式,為了防止9244輸入飽和,將R6和R7改為1k。8488輸出共模電壓為2.048V,9244與8488共用同一個參考電壓,因此9244的零點即為8488的零點。

三、軟件設計

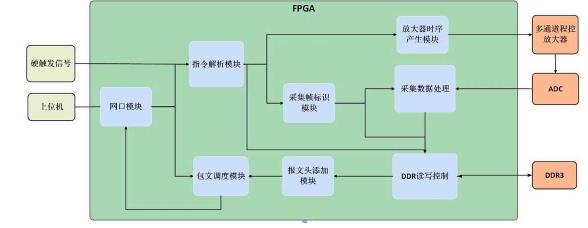

3.1FPGA工程架構

FPGA工程架構如圖10所示:

圖10FPGA工程架構

3.2FPGA工程功能

上位機或者硬件信號控制ad8488芯片的采集使能和復位,打包ad采集128通道的所有數據,并通過網口傳輸到上位機。

上位機可配置ad采集的幀數量、每幀采集輪次、各通道采集數據閾值;

上位機可配置ad8488芯片采集時序和采集增益;

上位機可配置重讀包文序號和重讀使能,支持重讀每次采集的任意AD數據包文;

支持上位機指令返回;

每采集完一幀數據就向上位機發送該幀數據的所有包文;

AD采集數據為0xff時替換為0xff(通道數據間的分隔符是0xff避免采集數據和分隔符混淆)。

3.3模塊介紹

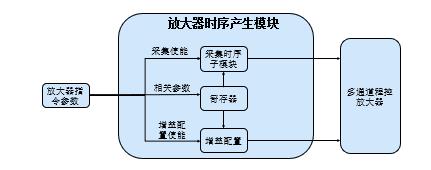

FPGA工程共分為四個模塊,分別是放大器時序產生模塊、采集

數據處理模塊、采集幀標識產生模塊、指令解析模塊,各模塊框圖如

下:

放大器時序產生模塊放大器時序產生模塊根據參數和放大器控制邏輯生成放大器控制和增益配置時序。

圖11放大器時序產生模塊

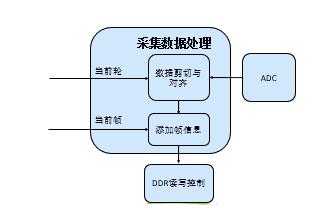

采集數據處理模塊采集數據處理模塊用于切除8488時序中不需要的ADC數據;根據8488時序,對應通道與ADC數據;不同通道之間添加分隔符;一幀數據采集完成后添加幀標識標簽。

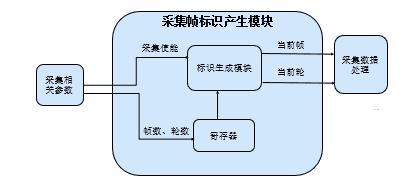

圖12采集數據處理模塊采集幀標識產生模塊采集幀標識產生模塊根據時鐘計算當前幀和當前輪。

圖13采集幀標識產生模塊

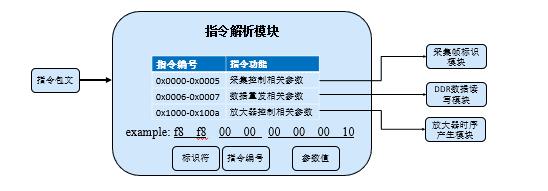

指令解析模塊指令解析模塊用于解析上位機下發的指令。指令格式數據長度短,需在包文后面補一定數量的0x00,避免包文過短被路由器丟掉。

圖14指令解析模塊

四、總結

AD8488和AD9244組合,對微弱電荷信號進行采集,不僅可以應用于高能物理方面,在壓電、質譜、能譜、射線等等。本系統配合CZT傳感器,在X射線探測上已經取得了初步驗證,證明本系統的設計合理,采集精度高,通道間串擾小,且裝置體積小巧,使用靈活。設計中還發現了工頻噪聲被ADC采集到的問題。具體處理方式有兩點:

4.1、系統改用鋰電池進行供電,直接排除工頻干擾。目前測試系統ADC底噪僅4bit,符合項目需求。

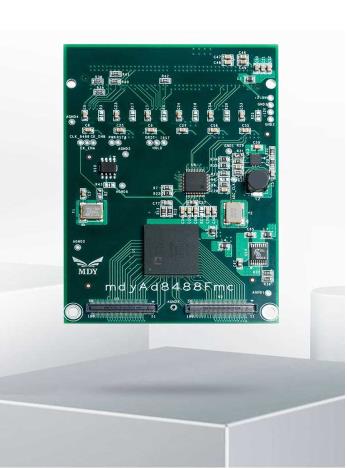

4.2、在數據處理時加入50Hz陷波處理。優點是硬件靈活,不需要硬件濾波。目前該采集系統已經設計成FMC子卡的形式,如圖15所示。該子卡配合明德揚MP5620開發板,即可實現128通道電荷采集功能,可以用來進行工程驗證,減少前期試錯成本。

圖15AD8488FMC子卡

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)