如果同學們的學習問題我們帖子里面沒有的,請第一時間聯系我微信同步:易老師13112063618

明德揚還做了抖音系列短視頻,感興趣可以關注明德揚抖音號:FPGA技巧分享(87481069842)內容不斷更新!點贊+關注,學習不迷路!

【問題1】DDR3那個課程,一般線速率能跑到多少?

答:本課程的DDR3內容,是基于XILINX K7芯片,使用的是VIVADO平臺。DDR3的時鐘頻率是800M。用戶側時鐘是200M。

【問題2】SDRAM和DDR3課程,使用是什么平臺?

答:SDRAM部分使用的是QUARTUS平臺,著重于講解SDRAM時序和SDRAM的接口設計。 DDR3部分,使用的是VIVADO平臺,著重于DDR3 IP的生成和上板驗證流程。DDR3的理論部分,基本上不涉及,建議可以參考SDRAM的理論部分。

【問題3】 使用DDR3 IP一定需要讀地址FIFO,讀數據FIFO,寫地址FIFO,寫數據FIFO來先進行數據緩存嗎?

答:這個理解是不對的。這里沒有跨時間域的信號傳輸的。因為IP核會產生一個本地時鐘,這個本地時鐘是可以直接采集數據的,假設為clk_ddr_local。用戶可以直接使用clk_ddr_local來往IP核傳輸數據。

好了,接下來再考慮一個場景:我有一組數據A,產生于時鐘域clk;A要寫到DDR,DDR的時鐘域是clk_ddr_local。自然地,A要跟時鐘域到clk_ddr_local,然后才能寫到DDR中,這就需要用到FIFO。

接下來考慮另一個場景:我有一組數據B,產生于時鐘域clk_ddr_local;B要寫到DDR,DDR的時鐘是clk_ddr_local。由于兩個時鐘域相同,直接寫就好了。(通常來說,這已經不屬于DDR的知識了,而是屬于跨時鐘域處理的知識,是FPGA工程師都應該知道的概念)。

【問題4】用戶邏輯控制DDR3讀寫的程序不是需要自己寫嗎?

答:官方一般提供了DDR3的IP核。用戶可以通過DDR3 IP核來進行DDR3芯片的讀寫。但是用戶需要寫邏輯來控制DDR3 IP核。

【問題5】課程里會講如何通過DDR3 IP像寫入圖像嗎?

答:課程中的SDRAM部分,會有例子講如何寫入圖像到SDRAM中,DDR3/4也是類似的。但由于每人的項目不同,所以需要學員根據自己情況來移植。

【問題6】如何知道ddr3里不空,可以讀取了?

答:DDR3和RAM一樣,是一個存儲器件,它的每個內部單元都存儲了當前的數據狀態值。但DDR3和RAM本身,是沒有“空”、“存有數據”,“數據滿”等概念的。只要給地址,它就會把當前地址的數據給到總線上,而且這個地址可以讀很多次。在設計的時候,是由設計師用自己寫邏輯來判斷DDR3是否為空。

【問題7】請問這個sdram的自動刷新命令發送后,是不是刷新的是所有bank的同一行都在執行刷新呀?也就是說刷新的是不同bank的同一行,是不是這樣理解?

答:是的。發送一個自動刷新命令,所有BANK同一行都會刷新。

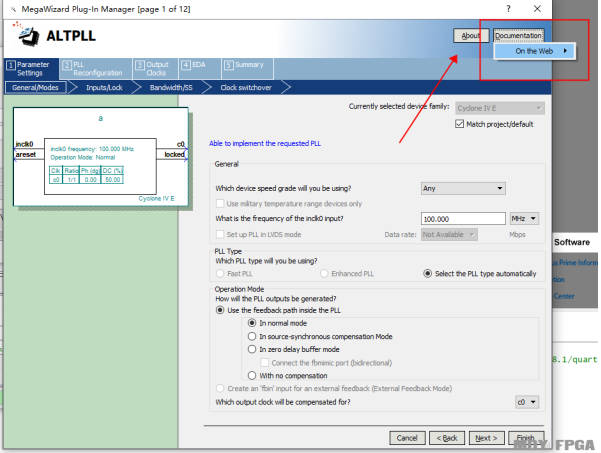

【問題8】請問有ddr3的IP核手冊嗎?(altera的)

答:IP核不同,界面會所不同,但一般都會提供下載鏈接的。VIVADO、ISE等,也是同樣的情況

【問題9】做一個用到ddr4的項目,有一個ddr3的例程,不知道怎么改成ddr4?

答:百度搜索找資料,按流程配置就好,這個我們沒有教程,只能看數據手冊

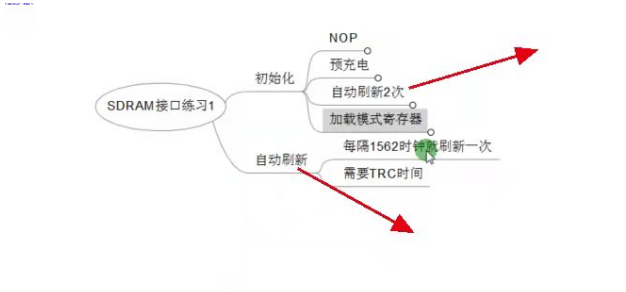

【問題10】下圖中的自刷新有啥區別?

答:上電后,要經過初始化,初始化中要有兩次刷新動作;當初始化完成后,才是每隔一段時間,要自刷新一次

【問題11】如下圖所示,為什么在接口中,一般要鎖存住地址addr、寫數據wdata等?不鎖存不行嗎?

答:如上圖所示,假設在第2~6時鐘時刻,addr的值為2,表示此時要寫地址2。本模塊收到此請求后,會在后面如第7~10時鐘,產生寫地址為“2”的時序。但注意,在第7~10,addr的值還是不是2呢?可能不是了。

【問題12】請問連接ddr3 ip核與mem_burst時,有些端口未定義。內些未定義的端口怎么辦?

答:

1. 本課程提示的案例,經過上板驗證是可以的,如果不可以,請及時向老師反映。

2. 本例程驗證過是可以的,因此例化時未連接的信號,就說明對本例程來說不用關心,不用使用。

3. 如果您要想關心這些信號,可以閱讀數據手冊,了解該信號含義。

【問題13】問題:請問老師xilinx FPGA的HR bank的 lvds接口可以驅動250Mhz DDR adc 嗎?我一直只能跑到100Mhz ,不知道是不是我的時序有問題?

答:

1、首先請確認使用的芯片是否支持該DDR的速率;

2、如果支持的話,請嚴格按照設計規范進行設計;

3、同時請檢查該開發板的pcb原理圖的設計是否合適,例如pcb的走線是否等長,或者pcb的板材是否合適、阻抗是否匹配......這些都會影響DDR的速率。

【問題14】問:?有 vivado 下 DDR模型和參數不?用于仿真?

答:vivado DDR可以生成對應的例程,可以用于仿真。具體操作步驟可以百度搜索一下,例如:Xilinx VIVADO中DDR3 IP核的使用(1)_朽月的博客-CSDN博客_xilinx ddr 自動刷新

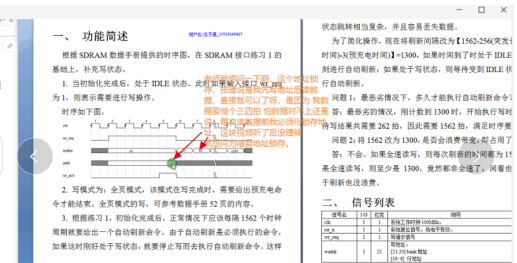

【問題15】問:SDRAM中將刷新時間改為1300的意義何在?

答:如果以1562個為周期,當時間到了之后,如果此時處于寫或讀操作狀態,就要等一段時間再進行刷新操作,這樣刷新間隔就會大于1562,不滿足要求。

【問題16】問:請問在邊緣檢測的項目中,輸入輸出數據是25M,SDRAM的工作時鐘是100M,這種情況下讀寫效能是多少呀?

答:SDRAM讀寫總線效能一般計算:SDRAM的工作時鐘 * 數據位寬 *70% 。(注意:其中70%是指減去sdram的一些操作占用后的效能,70%的數值是經驗之談,請根據實際情況變更數值)

【問題17】問:SDRAM工程中,讀寫請求是一個脈沖,還是連續的電平?

答:在MDY自定義的接口中,讀寫請求是一個持續為高的電平信號,一直拉高直到模塊響應為止。拉高一個電平為表示讀寫一次。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)