如果同學們的學習問題我們帖子里面沒有的,請第一時間聯系我微信同步:易老師13112063618

明德揚還做了抖音系列短視頻,感興趣可以關注明德揚抖音號:FPGA技巧分享(87481069842)內容不斷更新!點贊+關注,學習不迷路!

【問題1】JESD204B專題課有交流群嗎?

答:購買此課后,均加入MDY的專題課交流群。

【問題2】交流群會解答哪方面的內容?

答: 購買此課程的同學,需要有一定的FPGA基礎,如一定的設計能力、驗證能力和調試能力。 本課程的交流群,將不會詳細解答基礎問題,例如VERILOG語法;自己修改的代碼,如果出錯,請自行定位。對于協議、架構等,如有問題,MDY都會詳細解答。

【問題3】FPGA的JESD204B參考文檔是PG066嗎?

答:是的。

【問題4】 AD9144的同步信號已經拉高了,這說明已經配置成功了?

答:要使用AD9144成功,可以依次檢查以下AD9144的幾個寄存器。地址OX470:該寄存器用于表示LANE有沒有檢測到K28.5同步字。如果說FPGA管腳配置錯誤、時鐘有問題、LANE速率有問題(例如雙方配置的LANE速率不同,一端為2G,另一端為2.5G;或者信號質量不高,傳輸有誤碼等),則讀到的值將不正確。 地址OX471:檢查是否所有的LANE都已經同步。如果地址0X470正確,本寄存器不正確,則可能是速率、時鐘有問題。 地址OX472:檢查checksum,即校驗和是否正確。如果說FPGA和AD9144的參數不同,或者是傳遞有錯誤,則此寄存器值不正確。地址OX473: 檢查ILAS。如果說此正確,基本上都正確了。

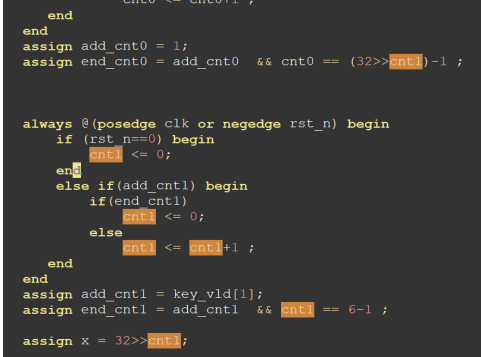

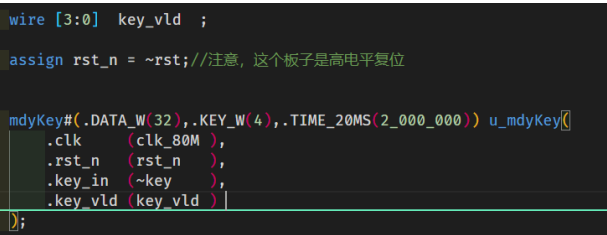

【問題5】頂層模塊jest204b_test中,下面的代碼是什么含義?

答: 本工程有一個功能,通過按下按鍵,可以改變信號的頻率。工程一共支持6種頻率,cnt1值為0~5,分別用來表示6種頻率。上面代碼中的cnt0控制頻率的,其是通過控制同一值重復的次數來達到控制頻率的目的,例如假設某信號值為01234為100M信號頻率, 讓每個點重復一次,即0011223344,信號頻率就變為50M。 cnt0的值根據cnt1來改變,例如當cnt1為0時,cnt0的值為0~31,當cnt1為1時,cnt0的值為0~15,當cnt2為2時,cnt0的值為0~7。

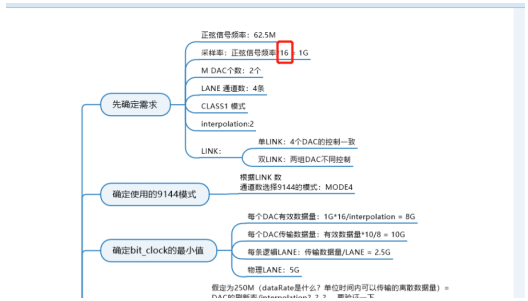

【問題6】如果要實現與工程中不同的分辨率和不同的采樣率(即輸出波形的頻率不同、分辨率不同),要怎么做?

答: 如果要改變波形的頻率,需要涉及到整個系統不同參數的調整,包括用于通信的lane的個數、時鐘頻率、IP核的寄存器配置和AD9144的寄存器配置等等。 具體可以參考視頻中,具體應該按下圖的步驟來分析:

上圖中,依次是確定需求,即您希望的信號頻率、采樣率DAC個數分別是多少,然后據此確定需要多少條LANE;進而確定AD9144的配置;lane的速率;sample時鐘等等。本課程有對應的視頻講解,可以詳細理解。請理解視頻中介紹的思想,從而應用到您自己的項目中。實用建議:建議您在我們提供的案例基礎上,每次改動一點點,看到正確效果后,再做下一下,最終完成最終的目標。

【問題7】案例中,插值為2的意義?為什么要插值?

答:插值,顧名思義,就是在兩個數據中間自動插入數據。例如要產生一個波形012345,不插值的情況下,FPGA必須要發送數據012345這幾個 數據給AD9144;而在插值為2時,FPGA只需要發送0246數據,然后AD9144自動補充135。本案例中,為什么要使用插值為2,是假設的一種需求情況。

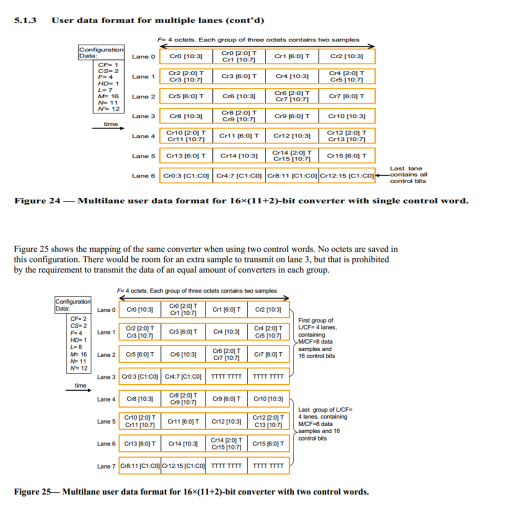

【問題8】在文檔《JESD204B協議》中,第52頁的下面兩個圖,為什么這兩者的CF不一致?CS又是什么?

答:CS是指一個SAMPLE中的控制位比特數,上面兩種情況,每個SAMPLE都加了2位的控制比特,即圖中的C1和C0。注意,圖中的“Cr0:3[C1:C0]”,是指Cr0的[C1:C0]+Cr1的[C1:C0]+Cr2的[C1:C0]+Cr3的[C1:C0]。CF是指一個FRAME CLK中的控制字個數,單位為字節。注意,這里的CF的限定條件是一個“FRAME CLK”。一個FRAME CLK,即上圖中的一列數據。

從第一個圖可以看出,第一列控制字是Cr0:3[C1:C0],共8比特,所以為CF=1。

從第二個圖可以看出,第一列控制字是Cr0:3[C1:C0]和Cr8:11[C1:C0],一列共有16比特,所以CF=2

【問題9】在講解需求時,下面的16是什么含義?

答:這里的16,是我們假設一個正弦波由16個采樣點組成,所以由信號頻率*16=采樣頻率。 當然,這里的16假設值,當您的正弦波是由32或者64,或者更大數組成時,當然就不同。我們這里是先確定需求。

【問題10】204b配置完了才正常工作還是不配置也能工作,配置完之后會改變工作方式?

答:都是需要配置完才能正常工作的。

【問題11】是否應該補充IP核的配置,為什么要那樣配?

答:1. 關于各個參數,如CS F M N等參數,在講解確定需求的視頻中,已經逐個分析出來。總的來說,是看AD9144文檔,看MODE后,根據MODE所推薦的參數來配置。

2. 得到上面參數后,請閱讀一下FPGA IP核的寄存器手冊,很簡單的,基本上是各個參數配上去就行了。

3. 配置代碼,可以看代碼解釋視頻,后面補充了。

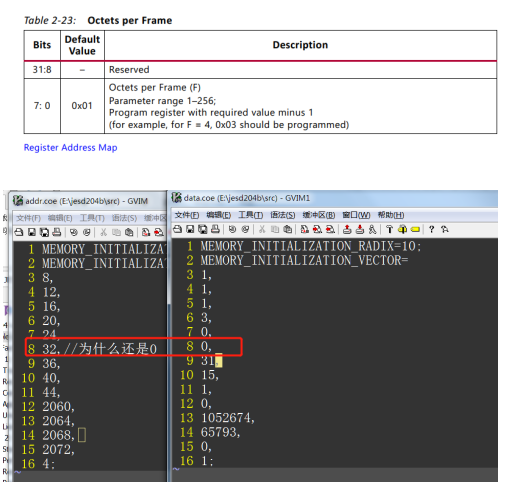

【問題12】204b配置文件里面有一個寄存器有疑惑,手冊里面寫的最小是1,但coe配置成0 。

答:寄存器中,“parameter range 1-256”,是指F這個參數的范圍是1-256。但后面有描述,此寄存值的值 = F-1,所以才填為0。這里描述有些歧義,但可以用這種方法排除:假設寄存器是1-256,那該寄存器是8位的,無法表示256,矛盾。

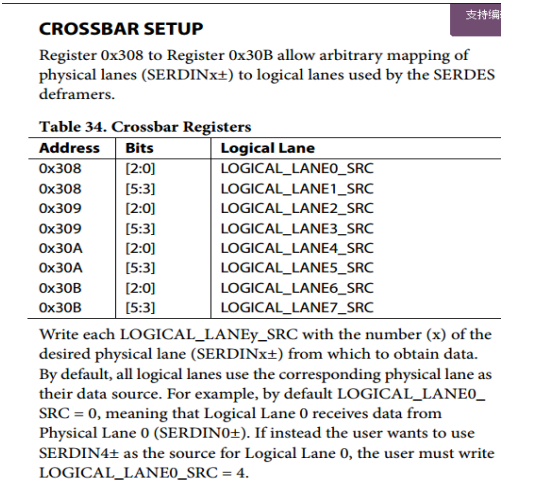

【問題13】在AD9144的0X308~0X30B這幾個寄存器,是用來選擇serdin和lan的關系的,這是如何對應的?

答:下面是這幾個寄存器的相關描述。

首先,明確概念,SERDIN0~7指的是AD9144芯片上定義的管腳,是物理的,可以去看管腳圖。LANE0~7,是指內部表示的LANE編號。

估計是為了靈活性,LANE0~7不是與SDRDIN0~7不是一個一個對應的,其對應關系是可以配置的,上面幾個寄存器就是起這種作用。例如,LANE0可以與SERDIN0對應,這個時候的0X308[2:0]=0,也可以和SERDIN4對應起來,這個時候0X308[2:0]=4。其次,理解了上面關系后。你可以根據實際情況來配置,例如,本案例中的AD9144子板,它的SERDIN0~3是沒有用的,只使用了SERDIN4~7,這是固定死的。然后內部的配置,您可以使用LANE4~7來對應SERDIN4~7,也可以使用LANE0~3來對應SERDIN4~7,這由您來決定,都是可以實現的。最后,再強調一下工程思維:芯片提供了很多功能,您用也可以,不用也可以,您會怎么做?你就選擇最簡單的來做,甚至就是忽視它存在,也就是使用默認值。

【問題14】JESD204B課程里包括AD和DA嗎?還是只是其中一個?

答:本課程只包括AD部分,并且是以AD9144為例來說明。注意不同AD和DA芯片,其使用方法都是不同的。本課程只講述一般思路,需要學員舉一反三使用。

【問題15】要得到16個點,插2,所以實際傳8個點;學習筆記里面生成的正弦波,由于插2了,實際是32個點,這么理解對么?

答:在DA輸出端如果16個點組成一個正弦波,插值為2的情況下,FPGA只需要傳輸8個點/正弦波。如果FPGA傳輸16個點/正弦波,插值為2的情況下,DA輸出端實際是32個點/正弦波。

【問題16】為什么v5版本是6.4Glane速率,而v7就是3.2Glane速率了,都是10~40M的正弦波啊?

答:LANE的速率,可以大于等于“需要的速率”,只要能保證傳輸即可。

【問題17】專題課實現的最高采樣率是多少?

答:專題課里有多個工程案例,實現的最高采樣率是1Gbps。理論上,AD9144是可以實現2.8G的,但課程沒有提供。

【問題18】JESD204B的licensing在哪里獲取?

答:請去官網獲取臨時licensing,鏈接如下:https://www.xilinx.com/products/intellectual-property/ef-di-jesd204.html。選擇:Evaluate ip選項,按提示操作即可。臨時licensing,獲取后,可以不聯網,然后正常生成bit文件。正式的licensing,需要購買,如果需要請向官方購買,MDY不提供正式licensing。至于臨時和正式的區分,暫時未知,目前來說不影響學習用途。

【問題19】用戶用破解的Vivado能不能使用 JESD204B的Ip?

答:可以使用。但注意,JESD204B的IP是臨時licensing,具體請看問題11.19。

【問題20】案例中的AXI時鐘必須是100M嗎?

答:不一定,滿足范圍即可。在設置IP核時,有提示范圍的。

【問題21】有沒有k7芯片許可證或者下載地址?在官網沒找到

答:官網licence的中心網址:https://www.xilinx.com/support/licensing_solution_center.html。這個license是跟機器綁定,需要客戶自行到官網申請,MDY提供不了文件。

【問題22】204B的每個時鐘發送的4個采樣點,是輸出波形里緊挨著的4個點嗎?還有9144輸出波形周期是如何控制的?怎樣算發送完了一個完整波形的數據?

答:這個可以看txdata的視頻講解。

【問題23】204B的教程目前只有發送的,沒有做接收的嗎?

答:我們課程是只有發送的,沒有接收的,不過接收方向的可以參考。

【問題24】使用204B的IP,為什么需要用到204B_PHY,是為了鏈接網絡口嗎,那如果不連接網絡口,是否就不需要使用204B_PHY這個IP了,只用204b的IP一個就夠了?

答:PHY只是接口傳輸作用,如果沒有接口的話,那自然可以不用。目前沒看到有這種使用場景。

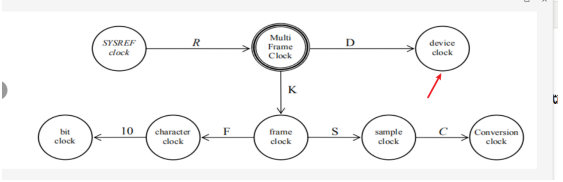

【問題25】關于時鐘計算,那個R是如何得到的?

答:R值只要是整數都是可以的。所以這個時鐘也可以等于Multiframe時鐘,也是可以的。不用設置寄存器。

【問題26】請問一下jesd課程的參考工程中:v7與與其他版本的不同是沒有拆除9144子板的cpu。請問這里的拆除具體指的是什么?難道v3v4v5不能直接把9144fmc插到k7上就能用?要另外做什么硬件準備嗎?

答:按照V7去做硬件即可。前面拆除是因為我們做項目時,就拿到一個拆除的硬件。

【問題27】204b,通過lane傳輸的時候,fpga不用單獨給DAC提供時鐘,而是通過CDR從lane數據線中恢復出時鐘,這樣理解對嗎?那還有output delay嗎?

答:是可以這樣理解,沒有output delay的。

【問題28】項目里的SPI時序沒有詳細講解,看不懂。

答:本課程定位為非基礎課程,SPI時序屬于基礎設計。如果想了解SPI時序理論,可以百度相關內容,資料很豐富的。 如果想了解MDY的SPI是如何實現的,可以參考如下資料:http://www.cqqtmy.cn/jishushipin/2019/1212/596.html, SPI內容在最后講述。

【問題29】老師,204b的input delay是SYSREF嗎?這個是怎么處理的。

答:本項目不需要時序約束,您描述的問題點也不清晰。

【問題30】204b是不是不能通過示波器抓取,那有什么方式知道lane的速率是2.5G?

答:配臺高級示波器,或者使用IBRT測試,具體的方法請百度。

【問題31】如果我這里有兩個9144芯片,他們之間如何同步呢?

答:

1.時鐘同步,采用同一個時鐘芯片,由這個時鐘芯片產生多路時鐘給這些AD9144,由于時鐘源是相同的,所以時鐘都是一樣的。這樣可以保證時鐘的同步。

2.由于都是一個FPGA發數據,按照JESD204B排列數據分配給各條LANE,這樣就可以了。

【問題32】JESD課程是用Veriiog代碼實現還是用XILINX的IP核?

答:該課程使用了IP核來實現

【問題33】是否包含有高速AD/DA的項目?最高速率是多少?有多少路?

答:激光工程項目中,包含有高速ADC AD9684,速率是500M,目前是支持一路的實現。 精密儀器項目中,包含有高速的DAC AD9144,目前實現的最高速率是1G,支持2路輸出。

【問題34】精密儀器項目中,AD9144的AD測量范圍,DA輸出的范圍,以及采樣率分別是多少?

答:AD9144是一款DAC芯片,所以沒有AD測量范圍。DA采樣率我們實現的是1G,實質可達1.8G。DA輸出范圍以及更多信息,請參考以下數據手冊。AD9144-FMC-EBZ RevB Schematic.pdf (79.85 KB, 下載次數: 0)AD9144.pdf (2.79 MB, 下載次數: 0)

【問題35】JESD204B課程中,是那種并口高速adc用的那種協議么?

答:不是高速并行口,而是高速串行口,即SERDES接口來實現,單根線的速率可達到10G。

【問題36】就業班企業項目里視頻拼接MIPI項目有用到IP核嗎?需要額外交IP核費用嗎?

答:MIPI項目是用的lattice芯片,lattice的此IP是免費的,學習此項目無需額外繳費。

【問題37】申請JESD的臨時License提示不符合出口規定,有沒有什么其它辦法?

答:換了個企業郵箱賬號就行了

【問題38】一,首先我得讀9156寄存器,二,我的讀9154{我自己的dac}三,用 dpg..現在dpg軟件駛不了,麻煩解答一下?

答:我們提供的例程,已集成在工程里面的,全部代碼是FPGA代碼。

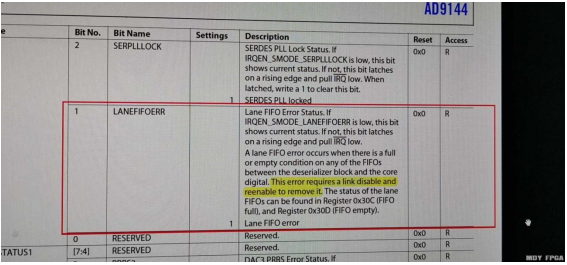

【問題39】請問9144用的是mose0,配置完后,CGS可以過,可以讀到寄存器470是FF,8個lane都收到了k28.5,但是寄存器023的bit1一直在01之間不停的跳動,代表FIFO的讀寫一直有錯誤,查看30c和30d也能看到錯誤標記,此時發送sysref的話,ILAS也能過,但是470,471,472,473都在不停的跳動,sync標記也是忽高忽低,此時鏈路不穩定,給tx核送數據,在頻譜儀上能看到9144的輸出,但是因為鏈路不穩定,輸出會不停的閃爍,理論上講,鏈路穩定的話,470.471.472.473都應該回讀FF才對,我想請教一下,是什么導致了9144配置完后fifo的讀寫標記一直報錯呢?也就是寄存器023的bit 1

答:如果是自己做的硬件板,則有可能是硬件的穩定性問題。請檢查硬件電路。

【問題40】請教一個問題,204b時序不行。12.5g,312.5M的核時鐘。一個dac時序違例不嚴重能工作,另一個不行,怎么處理

答:解決時序違例,其思路是減少組合電路邏輯。如果確實無法減小,那就只能降低時鐘頻率了。您使用的315.5M是工作時鐘的話,那確實是太高了,建議可以將工作時鐘降為156.25M

【問題41】請問按鍵是有4位., 但代碼中只使用了0位和1位, 這按鍵有沒有順序要求, 先按哪個再按哪個? 然后這個這個按鍵信號作為使能信號, 是只持續一個時鐘, 還是需要一直為高?

答:先按啟動有效的按鍵,再按改變頻率的按鍵,具體請看使用說明。

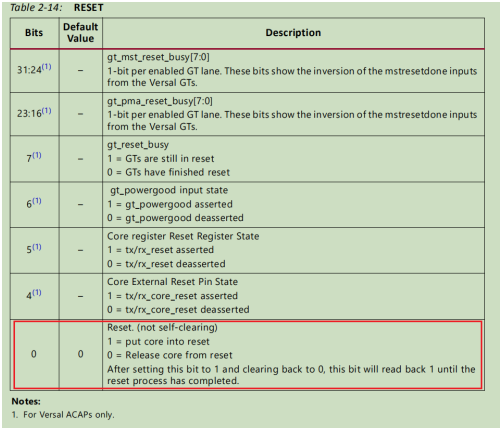

【問題42】請問在給JESD204C IP核配置的時候,讀取0x020 RESET寄存器的值,讀到的值是0x081,說明這個IP一直處于復位狀態,無法從復位狀態退出,可能是什么問題呢?

答:檢查一下所有的時鐘和復位信號,一般都是跟這些信號有關

【問題43】請問FPGA中的204B IP核,其配置是在哪里定義?

答:JESD204B的IP核配置,其地址在addr.coe文件中定義;其寄存器值在data.coe文件中定義。

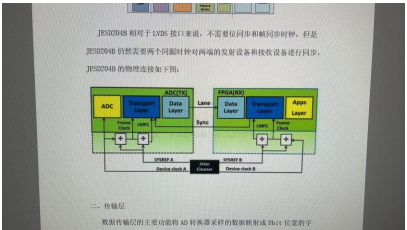

【問題44】device clock是什么意思?

答:可以認為是AD9516給FPGA的一個多幀時鐘,用于同步多幀的,可以認為D個多幀就發一個上升沿,這樣就好同步了。具體有一個視頻,可以看JESD204B協議04_實踐_協議各個時鐘的關系。

【問題45】:課程提供的上位機軟件是直接和dac連接用于檢測dac里寄存器的值嗎?還是dac通過傳數據到fpga通過fpga連接呢?

答:

做法1:上位機將寄存器配置值寫到FPGA,FPGA再寫到DAC里。

做法2:FPGA內部有配置表,上電后自動配置DAC的寄存器。 以上兩種方法都有。

【問題46】:如果是通過fpga連接的,是走的uart還是ethernet呢?

答:走的是網口。

【問題47】:vc707可不可以兼容我們的程序?

答:只要有HPC接口的,均支持

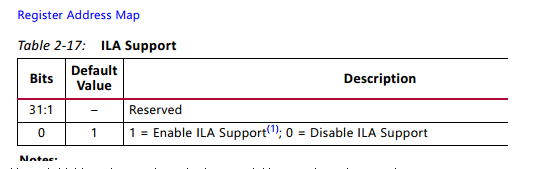

【問題48】:是不是地址8的ILA support設為1就代表在CGS之后開啟ILAS的功能?

答:該地址設為1,表示啟動ILA功能,設為0表示不啟用。

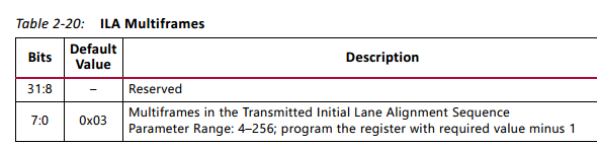

【問題49】:地址20的ILA multiframe是選擇ILAS一共發送幾組8位數據?我們設為3就代表發送4組8位數據?

答:這里不是以8位數據為音位,而是multiframe為單位。所以設為3,表示發送4個多幀數據。

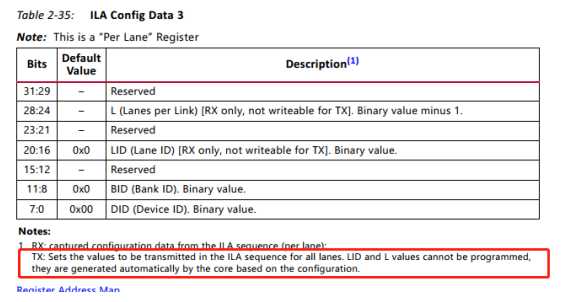

【問題50】:地址2060和2072的ILA config data 3 和 6 功能似乎是Sets the values to be transmitted in the ILA sequence for all lanes. 這兩個寄存器是用于設置ILAS發送的數據嗎?兩個寄存器都是0那發送的ILAS是全0,還是某個默認值?我看到網上有說是k28.0到k28.4順序發送的,但我看我的一個TI的dac好像默認是0x1C也就是K28.0

答:這里是設置需要的L、BID、LID和DID等參數。從字面上理解,發送方向就會把這些數據當成ILA數據發給對端。按真實要求配置即可。設了什么值,就會打包成對應數據發送給對端。至于如何打包,我這還沒有研究。

【問題51】:multiframe包含幾個frame?

答:這個每個工程不同,是可以靈活設計的參數,并且是與時鐘頻率、其他參數相關聯的。

【問題52】:BID這些參數具體就要從DAC那邊找到對應的然后兩邊匹配就可以了,是嗎?

答:BID DID 這些,兩邊匹配即可。

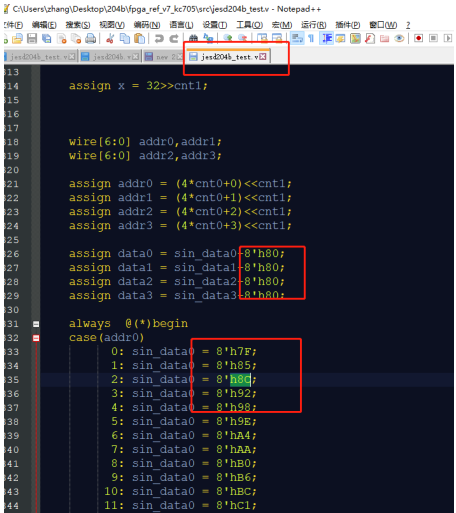

【問題53】麻煩問一下這個sin_data數據是怎么來的?自己造的數據嗎?

答:sin_data是正弦波的數據,該正弦波數據用matlab產生,模塊這里是轉化成verilog語言后的。

【問題54】減得那個8'h80是什么意思呢?為什么要減那個8'h80呢?

答:如圖紅色波形所示,該正弦波數據用8bit位寬表示,0~8'hff是它的幅度值范圍,中間的幅度值為8'h7f。 而在工程需求里,接口要求輸出的正弦波數據為補碼形式,那么正弦波的補碼波形如圖藍色波形所示, 補碼表示的最高點數值為8'h7f,最低點數值8'h80。對于數值8'h80+1=8'h01,8'h80-1=8'h7f,那么將正弦波數據sin_data-8'h80得到的就是如圖藍色的波形數據,也是一個補碼的數據。

【問題55】問題:請問jesd204 phy能選擇具體某一個quad嗎?具體如何選?

答:JESD204 PHY是可以選擇QUAD的,在IP核界面里可以選擇使用哪個,具體可以教程里的視頻

【問題56】JESD204B課程是ADC采樣,還是DAC采樣?(模數轉換是ADC,數模轉換是DAC)

答:是DAC采樣

【問題57】Jesd204B那個項目里的以太網通信是不是沒有調用MAC ip核,自己寫的

答:是的。該代碼沒有調用IP核,純RTL實現,模塊名為gmii

【問題58】fmcAD9144模塊從jp2送入AD9516的時鐘信號需要多大幅值的?1.8V夠嗎?

答:一般JP2的時鐘幅值為1.5V。1.8V也是可以的

【問題59】204B延遲高嗎?

答:延遲沒有實測,但從理論上來說,延遲是不高的。 通常對于這種應用來說,對延遲的要求也不會太嚴苛

【問題60】問:這個sysref信號必須由外部提供嗎?我們板子沒有這個信號,能不能用device clk這個信號分頻得到?

答;這里的核心思想是:

1.時鐘要穩定;

2. 兩邊都是完全同頻同步的時鐘

【問題61】問:老師我想問一下jesd項目里的9516和9144的配置視頻里講的是通過ACE工具和上位機軟件配置的,那vivado程序中又有配置模塊,這是怎么回事?

答:前期工程是由上位機配置的,后面提供的工程 由內部模塊配置的

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)