verilog是什么

Verilog一般指Verilog HDL。Verilog HDL是一種硬件描述語言(HDL:Hardware DescripTIon Language),以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。

Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design AutomaTIon公司(該公司于1989年被Cadence公司收購)開發。兩種HDL均為IEEE標準。

Verilog發展歷史

1、1981年Gateway AutomaTIon(GDA)硬件描述語言公司成立。

2、1983年該公司的Philip Moorby首創了Verilog HDL,Moorby后來成為Verrlog HDL-XL的主要設計者和Cadence公司的第一合伙人。

??3、1984-1985年Moorby設計出第一個關于Verilog HDL的仿真器。

??4、1986年Moorby對Verilog HDL的發展又做出另一個巨大的貢獻,提出了用于快速門級仿真的XL算法。

??5、隨著Verilog HDL-XL的成功,Verilog HDL語言得到迅速發展。

??6、1987年Synonsys公司開始使用Verilog HDL行為語言作為綜合工具的輸入。

??7、1989年Cadence公司收購了Gateway公司,Verilog HDL成為Cadence公司的私有財產。

??8、1990年初Cadence公司把Verilog HDL和Verilog HDL-XL分開,并公開發布了Verilog HDL.隨后成立的OVI(Open Verilog HDL InternaTIonal)組織負責Verilog HDL的發展,OVI由Verilog HDL的使用和CAE供應商組 成,制定標準。

??9、1993年,幾乎所有ASIC廠商都開始支持Verilog HDL,并且認為Verilog HDL-XL是最好的仿真器。同時,OVI推出2.0版本的Verilong HDL規范,IEEE接收將OVI的Verilog HDL2.0作為IEEE標準的提案。

??10、1995年12月,IEEE制定了Verilog HDL的標準IEEE1364-1995.

??任何新生事物的產生都有它的歷史沿革,早期的硬件描述語言是以一種高級語言為基礎,加上一些特殊的約定而產生的,目的是為了實現RTL級仿真,用以驗證設計的正確性,而不必像在傳統的手工設計過程中那樣,必須等 到完成樣機后才能進行實測和調試。

verilog的特征??

1、采用verilog HDL 進行電路設計的最大優點是設計與工藝無關系,這使得設計在進行電路設計時可以不必過多考慮工藝實現時的具體細節,只需要根據系統設計的要求施加不同的約束條件,即可設計出實際電路。??

2、能夠在每個抽象層次的描述上對設計進行仿真驗證,及時發現可能存在的設計錯誤,縮短設計周期,并保證整個設計過程的正確性;??

3、能夠在不同的抽象層次上,如系統級、行為級、RTL (RegisterTransfer Level) 級、門級和開關級,對設計系統進行精確而簡練的描述。

Verilog邏輯門級描述??

邏輯門級描述的抽象級別較低,僅次于晶體管級。

實際的硬件電路往往都是以邏輯門級網表作為基礎構建的,而設計人員常常會在進行更高抽象級別的設計。

盡管如此,邏輯門級的設計還是更接近真實電路形式。

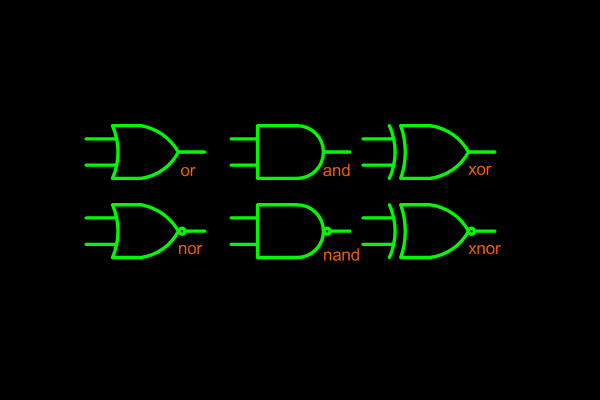

Verilog提供了一系列邏輯門原語(Primitive)供用戶使用。例如,非(not)、與門(and)、或門(or)、與非門(nand)、或非(nor)、異或(xor)、同或(xnor)。邏輯門原語和模塊類似,可以通過實例引用的方式使用。

Verilog晶體管級描述

Verilog能夠在低抽象級別對電路進行描述,是它的一個重要特點。

Verilog中提供了多種晶體管級(也稱開關級)元件類型,包括N型金屬氧化物半導體場效應管(關鍵字為nmos)、P型金屬氧化物半導體場效應管(關鍵字為pmos)、互補式金屬氧化物半導體(關鍵字為cmos)、帶阻抗的互補式金屬氧化物半導體(關鍵字為rcmos)、電源單元(關鍵字為supply1)、接地單元(關鍵字為supply0)等。所有的晶體管都可以設置延遲屬性。設計人員可以利用這些低抽象級元件構建所需要的邏輯門或直接構成其他高級組件。

verilog的用途

Verilog HDL就是在用途最廣泛的C語言的基礎上發展起來的一種硬件描述語言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首創的,最初只設計了一個仿真與驗證工具,之后又陸續開發了相關的故障模擬與時序分析工具。1985年Moorby推出它的第三個商用仿真器Verilog-XL,獲得了巨大的成功,從而使得Verilog HDL迅速得到推廣應用。1989年CADENCE公司收購了GDA公司,使得VerilogHDL成為了該公司的獨家專利。1990年CADENCE公司公開發表了Verilog HDL,并成立LVI組織以促進Verilog HDL成為IEEE標準,即IEEE Standard 1364-1995.

Verilog HDL的最大特點就是易學易用,如果有C語言的編程經驗,可以在一個較短的時間內很快的學習和掌握,因而可以把Verilog HDL內容安排在與ASIC設計等相關課程內部進行講授,由于HDL語言本身是專門面向硬件與系統設計的,這樣的安排可以使學習者同時獲得設計實際電路的經驗。與之相比,VHDL的學習要困難一些。但Verilog HDL較自由的語法,也容易造成初學者犯一些錯誤,這一點要注意。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)