1、 仿真的目的:

??在軟件環(huán)境下,驗(yàn)證電路的行為和設(shè)想中的是否一致。

??2、 仿真的分類:

??a) 功能仿真:在RTL層進(jìn)行的仿真,其特點(diǎn)是不考慮構(gòu)成電路的邏輯和門的時(shí)間延遲,著重考慮電路在理想環(huán)境下的行為和設(shè)計(jì)構(gòu)想的一致性;

??b) 時(shí)序仿真:又稱為后仿真,是在電路已經(jīng)映射到特定的工藝環(huán)境后,將電路的路徑延遲和門延遲考慮進(jìn)對(duì)電路行為的影響后,

來比較電路的行為是否還能夠在一定條件下滿足設(shè)計(jì)構(gòu)想。

??3、 功能仿真的目的:

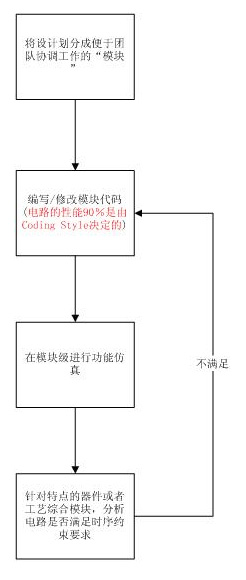

a) 設(shè)計(jì)出能工作的電路:因此功能仿真不是一個(gè)孤立的過程,其和綜合、時(shí)序分析等形成一個(gè)反饋工作過程,只有這個(gè)過程收斂,各個(gè)環(huán)節(jié)才有意義。而孤立的功能仿真通過是沒有意義的,如果在時(shí)序分析過程中發(fā)現(xiàn)時(shí)序不滿足需要更改代碼,則功能仿真必須從新進(jìn)行。因此正確的工作流程是:

b)代碼排錯(cuò):功能仿真是代碼排錯(cuò)的最重要的手段之一。

??4、 modelsim的高級(jí)功能:Code Coverage

??a) 代碼覆蓋率是驗(yàn)證激勵(lì)是否完備,檢驗(yàn)代碼質(zhì)量的一個(gè)重要手段。測(cè)試激勵(lì)的代碼覆蓋率至少要達(dá)到95%以上,

才能基本認(rèn)為代碼在邏輯上是通過質(zhì)量控制的,才能進(jìn)入綜合步驟;

??b) 代碼覆蓋率是保證高質(zhì)量代碼的必要條件,但卻不是充分條件。即便代碼行覆蓋和分支覆蓋都能夠達(dá)到100%,

也不能肯定的說代碼已經(jīng)得到100%的驗(yàn)證。除非所有的分支覆蓋都能夠進(jìn)行組合遍歷。

??c) 在大的設(shè)計(jì)中,如果想通過一個(gè)激勵(lì)就驗(yàn)證完一個(gè)設(shè)計(jì)或者模塊是不現(xiàn)實(shí)的。一方面是從邏輯功能上很難做到;

另外一方面是因?yàn)槿绻谝粋€(gè)激勵(lì)中包括了各種情況,整個(gè)仿真過程的速度會(huì)隨著計(jì)算機(jī)內(nèi)存的消耗而成線性下降,效率低下。

??d) 通常的做法是每一個(gè)激勵(lì)只驗(yàn)證電路功能的某個(gè)方面。整個(gè)電路的功能驗(yàn)證由數(shù)個(gè)激勵(lì)共同完成。在這種驗(yàn)證方法中代碼覆蓋率更顯重要,

因?yàn)榭梢酝ㄟ^代碼覆蓋率來控制激勵(lì)對(duì)功能的覆蓋程度。

??e) modelsim的Code coverage不但能記錄各個(gè)激勵(lì)對(duì)代碼的“行覆蓋”和“分支覆蓋”,而且能夠?qū)⒏鱾€(gè)激勵(lì)的覆蓋記錄進(jìn)行合并,做到對(duì)覆蓋率的全面監(jiān)測(cè)。

??f) 演示。。。。。。。。。。。。。。。。。。。。。。。。

??5、 Debussy:仿真輔助調(diào)試工具:

??a) 看仿真波形無疑是代碼排錯(cuò)的主要手段,在 Modelsim中的波形窗口在大的仿真中有如下缺陷:

a.只能顯示出在仿真前設(shè)置好的信號(hào)波形,如果在仿真完成后想觀察其他的信號(hào),唯一的辦法就是添加需要觀察的信號(hào)從新開始仿真。

b、波形只是簡(jiǎn)單顯示,和代碼沒有對(duì)應(yīng)和關(guān)聯(lián)關(guān)系,不能借助波形直觀的調(diào)試代碼;

c、如果觀察的信號(hào)太多,由于其是實(shí)時(shí)全信號(hào)顯示,在仿真時(shí)間較長(zhǎng)后,仿真速度明顯減慢,屏幕的刷新速度也明顯減慢。

??b) 這些缺點(diǎn)不單Modelsim有,其他的優(yōu)秀仿真工具也有,而且歷史由來以久,因此很早人們就提出了“先轉(zhuǎn)儲(chǔ)后觀察調(diào)試”

方法,在verilog語言中以$dumpXXX開頭的系統(tǒng)函數(shù)就是做波形轉(zhuǎn)儲(chǔ)用的。就是先將波形先存在文件中,等仿真結(jié)束后在調(diào)出來顯示觀察和調(diào)試。

??c) 這種觀察功能很多EDA工具都有,并不足為奇;但Debussy的獨(dú)特之處在于,它不但能顯示波形,而且還能非常智能化的將波形中的任何一個(gè)變化和引起這個(gè)變化的RTL代碼聯(lián)系起 來,使代碼排錯(cuò)的效率大幅度提高。在原來IC所的一個(gè)大型項(xiàng)目中,由于引進(jìn)了Debussy,使調(diào)試效率至少提高了3倍。

??d) 先介紹verilog語言中的轉(zhuǎn)儲(chǔ)系統(tǒng)函數(shù)。其實(shí)轉(zhuǎn)儲(chǔ)函數(shù)就是一種典型的文件操作函數(shù),最為常用的為一下幾種:

i. $dumpfile(“filename.vcd”):打開一個(gè)文件準(zhǔn)備轉(zhuǎn)儲(chǔ)波形數(shù)據(jù);

ii. $dumpall:轉(zhuǎn)儲(chǔ)所有信號(hào)的波形數(shù)據(jù);

iii. $dumpvars:轉(zhuǎn)儲(chǔ)層次信號(hào);

iv. $dumpon:開始轉(zhuǎn)儲(chǔ);

v. $dumooff:停止轉(zhuǎn)儲(chǔ);

??e) 演示Modelsim轉(zhuǎn)儲(chǔ)功能

??f) 演示Debussy工具中的輔助調(diào)試功能;

??6、 SDF反標(biāo)注

??a) SDF是一種標(biāo)準(zhǔn)延時(shí)格式文件,用于記錄綜合布線后電路的線延遲和門延遲信息。如果在仿真輸出的波形上疊加上這些信息,將使波形更接近實(shí)際。

??b) 演示。。。。。。。。。。。。。。。。。。。。。。。。。。

??c) 但是由于電路已經(jīng)被綜合布線過,原來的RTL代碼的邏輯層次和代碼命名都已經(jīng)發(fā)生變化,即便看到波形也很難直接對(duì)應(yīng)到RTL代碼上,因此后仿真來確定電路是否符合要求的方法已經(jīng)逐漸被新的方法所代替。 另外還有后仿真速度緩慢也是一個(gè)主要原因。新的方法是:時(shí)序分析、靜態(tài)時(shí)序分析、形式驗(yàn)證。

7、 一個(gè)重要的觀念:電路的性能取決于電路構(gòu)思和Coding Style:

??a) 經(jīng)常有人說“不要用寫軟件的方法去寫硬件”,或者說“要用樸實(shí)無華的語言風(fēng)格來寫代碼”,這些說法只是描述了事務(wù)的表明現(xiàn)象,并沒有真正指出問題的真正癥結(jié)所在;

??b) RTL描述語言,雖然是一種語言,但它是描述RTL的語言,所以其著眼點(diǎn)是電路實(shí)現(xiàn)而非邏輯推理;RTL就是電路在寄存器層的一種表現(xiàn),

雖然已經(jīng)不像門級(jí)那樣具體,但也沒有抽象到邏輯層。

??c) 因此寫代碼的真正正確的方法是:在大腦中構(gòu)思出電路的結(jié)構(gòu),然后用代碼把它點(diǎn)滴不漏的表現(xiàn)出來,而不是先寫一些只是邏輯上行得通的代碼等待工具幫你綜合成能實(shí)現(xiàn)的電路。

工具永遠(yuǎn)只能做繁重而低級(jí)的工作,至少要比人的工作低級(jí),這是未來 幾百年內(nèi)不會(huì)改變的公理。因此如果你的電路性能不好,說明你對(duì)如何實(shí)現(xiàn)電路還沒有清晰的思路。

??d) 不要只使像通過提高器件的速度等級(jí)來使你的電路達(dá)到要求,恰恰相反,正確的方法是:如果你的電路在第一次綜合后已經(jīng)有80%的路徑滿足時(shí)間要求了,

那么就不要想著用更快的器件,而應(yīng)該考慮改變你的電路拓?fù)浣Y(jié)構(gòu)和設(shè)計(jì)構(gòu)架,來使另外的 20%逐漸達(dá)到要求。

溫馨提示:明德?lián)P2023推出了全新課程——邏輯設(shè)計(jì)基本功修煉課,降低學(xué)習(xí)FPGA門檻的同時(shí),增加了學(xué)習(xí)的趣味性,并組織了考試贏積分活動(dòng)

http://www.cqqtmy.cn/ffkc/415.html

(點(diǎn)擊→了解課程詳情?)

明德?lián)P除了培訓(xùn)學(xué)習(xí)還有項(xiàng)目承接業(yè)務(wù),擅長(zhǎng)的項(xiàng)目主要包括的方向有以下幾個(gè)方面:

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(IMX472 IMX492)

3. PCIE采集系統(tǒng)

4. 圖像項(xiàng)目

5. 高速多通道ADDA系統(tǒng)

6. 基于FPGA板卡研發(fā)

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關(guān)信息可以聯(lián)系:易老師13112063618(微信同號(hào))