最近公司承接了一個車載視頻拼接的項目,該項目使用到了LVDS高速接口和DDR3接口,攝像頭采集的視頻圖像數據需要先存入DDR3中然后與通過LVDS傳輸的主機視頻數據進行拼接輸出,最終在屏幕上顯示畫中畫的效果。在調試DDR3的過程中,我有一些使用心得,特分享給大家。

在之前的文章中我已經介紹過Lattice DDR3的IP核生成使用方法,以及接口信號。也許有許多人不是很明白,明明有DDR3的IP核,為什么還要添加這么一個接口模塊,添加了這么一個接口模塊主要是用來做什么,需要它設計哪些信號?

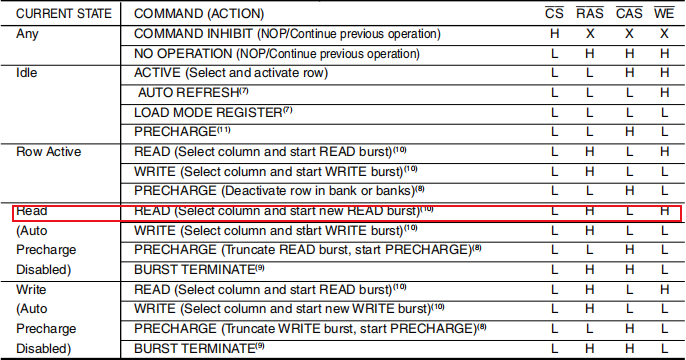

圖中用紅線標記起來的地方就是FPGA與外部DDR3通過引腳連接的接口信號,如果我們通過FPGA內部產生數據并將其送入DDR3中后讀出,就是通過這些引腳來傳輸信號的。我們使用SDRAM進行存儲,是直接控制這些輸出信號如CAS、RAS、CKE等控制SDRAM讀寫以及其他各操作的,如下圖就是SDRAM的輸出控制信號,通過FPGA內部設計CS、RAS、CAS、WE這些信號,可以讓SDRAM實現對應的操作。比如我們設計一個SDRAM讀操作,那么我們就需要設計CS、RAS、CAS、WE分別為0、1、0、1,SDRAM通過引腳接收到這些信號,便會產生對應的操作,即打開一個新的列地址并開始一個新的突發讀操作。

與設計SDRAM接口不同的是,我們在使用DDR3時,是不需要我們親自設計這些輸出信號, 因為我們調用的DDR3 IP核已經幫我們內部封裝好了這些指令,我們需要設計的是輸入IP核的那部分接口信號,來告訴IP核我們想讓DDR3進行工作的模式以及需要DDR3進行的操作。在設計這個接口模塊的時候,我們需要設計的就是圖1左側接口的那部分信號,各信號的功能以及時序在數據手冊上有詳細的說明(在我前面的文章中也有詳細的介紹),這需要我們一邊對照著數據手冊一邊進行設計,具體的設計方法我將會在接下來的文章中繼續介紹。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)