本文為明德揚原創文章,轉載請注明出處! 作者:云哥哥

1.PCIE的發送和接收數據

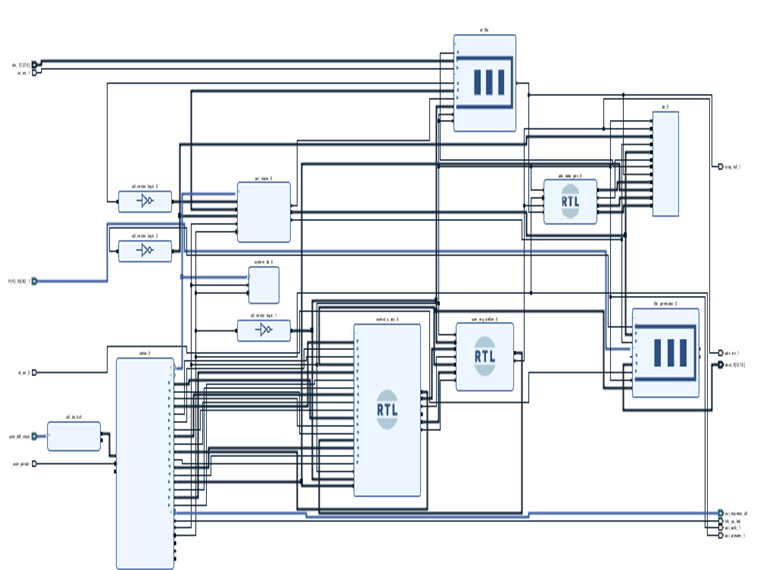

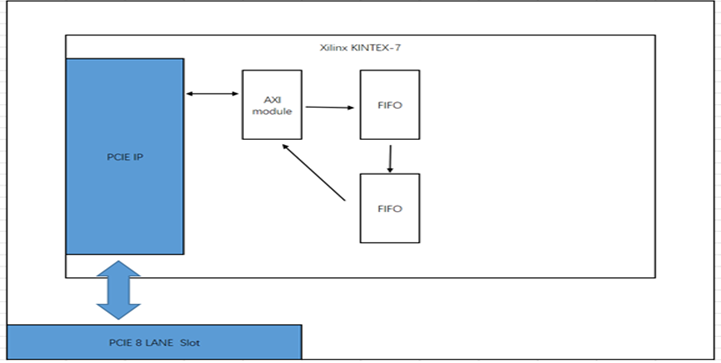

本工程的目的是在XC7K325tffg的平臺上實現pcie的數據發送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的結構:

架構

各個模塊的作用

PCIE部分結構圖

這是PCIE IP核,主要用來發送數據,發送引擎主要負責將待發送數據按照PCIE協議組織成不同類型的TLP數據包,并發送給PCIE IP核;發送DMA控制模塊主要負責把DDR3中讀取的數據轉換成TLP格式,并傳送給發送引擎;接收引擎用于從PCIE IP核接收不同類型的TLP數據,接收DMA控制模塊用于實現存儲器讀請求包的發送流量控制及接收數據位寬的轉換;DMA狀態控制寄存器模塊主要用來解析來自PC對模塊內部寄存器的命令和配置,并通知發送引擎模塊、接收引擎模塊及其他模塊作出相應執行。

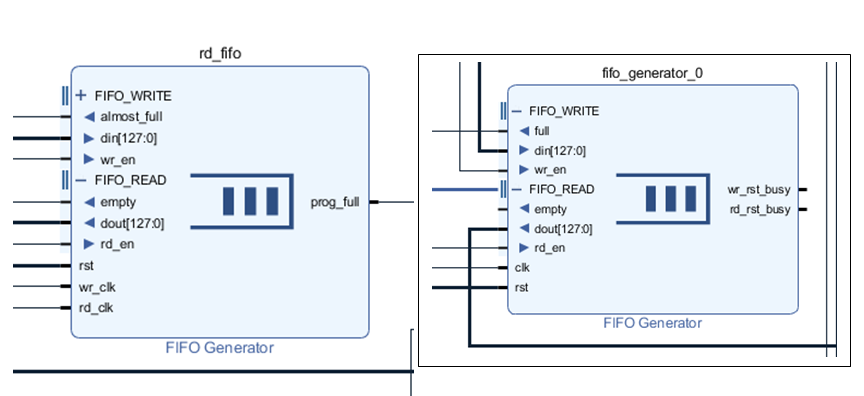

圖表 SEQ 圖表 * ARABIC 1

圖表一中 左圖Rd_fifo是數據寫入緩存模塊,右圖是讀出緩存數據模塊。

Fifo:先入先出隊列。數字電路設計中所說的fifo實際是指fifo存儲器,主要用于數據緩存和異步處理,fifo存儲器緩存數據也遵循先入先出的原則。Fifo本質是一個RAM,它與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀寫數據。

信號列表

名稱 | 方向 | 位寬 | 說明 |

FIFO_read_1_empty | o | 1 | 讀fifo的空信號指示 1:讀fifo里面沒有數據 0:讀fifo里面有數據 |

FIFO_READ_1_rd_data | o | 128 | 讀fifo數據的輸出 |

FIFO_READ_1_rd_en | i | 1 | 讀fifo的使能 1:讀出讀fifo里面的數據 0:不讀數據 |

adc_en_1 | o | 1 | 接收到的寄存器使能 1:寄存器0x0收到數據為0x01 0:寄存器0x0收到數據為0x00 |

Axi_aclk_1 | o | 1 | PCIE 對外提供的用戶時鐘 |

axi_aresetn_1 | o | 1 | Pcie對外提供的復位 |

din_1 | i | 128 | 用戶側想要發送的數據接口 |

Lnk_up_led | o | 1 | Pcie連接指示信號 |

Pci_express_x8_rxn | i | 8 | Pcie的接收管腳n端 |

Pci_express_x8_rxp | i | 8 | Pcie的接收管腳p端 |

Pci_express_x8_txn | o | 8 | Pcie的發送端n端 |

Pci_express_x8_txp | o | 8 | Pcie的發送端p端 |

pcie_diff_dock_clk_n | i | 1 | Pcie時鐘信號n端 |

Pcie_diff_dock_clk_p | i | 1 | Pcie時鐘信號p端 |

Pcie_perstn | i | 1 | Pcie得復位管腳 |

Prog_full_1 | o | 1 | 寫fifo的滿信號 |

wr_en_1 | i | 1 | 寫fifo的寫使能 |

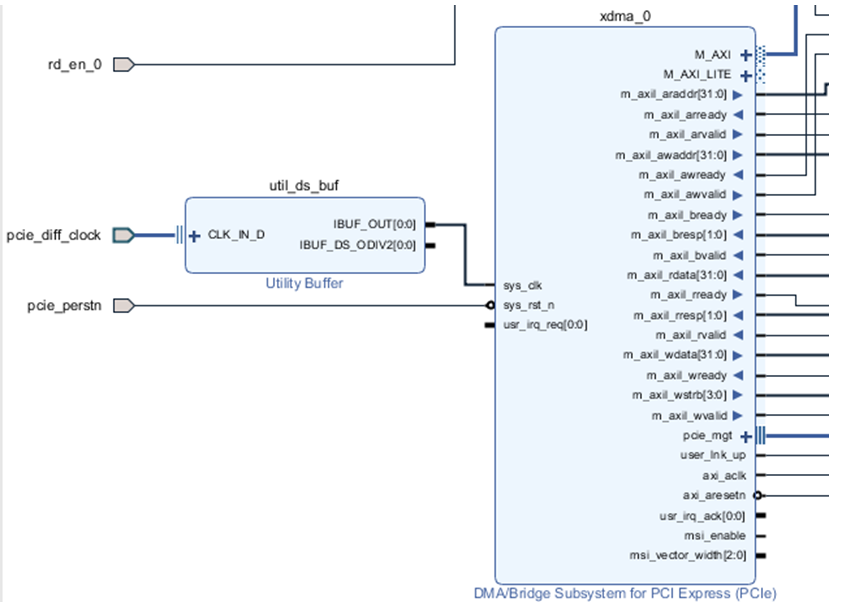

以上就是pcie xdma ip核介紹,想要學習更多內容的同學,可以加Q:1465617980 云哥哥 了解更加專業的知識!

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)