明德揚(MDY)在2022年承擔了多個高速ADC研發項目,今天給大家分享下高速ADC噪聲系數計算方法。

首先在AD選型時,我們最關心的一個指標就是AD的信噪比(SNR),這項指標直接影響了抗干擾板的噪聲系數。噪聲系數(NF)的計算過程如下:

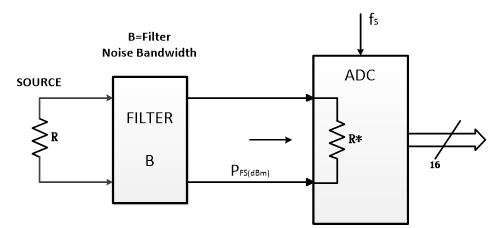

圖1為ADC采樣過程的一個簡易模型。該模型假定一個電阻為R的信號源作為ADC的輸入。由于有ADC采樣時鐘的限制,信號源與ADC之間相當于接入了一個奈奎斯特帶寬(DC至fS/2)的濾波器。同時,這也限制了輸入信號的噪聲帶寬。設該帶寬為B。在ADC端的電阻R*為ADC的輸入阻抗。由于我們設計電路時已經根據數據手冊提供的參數對輸入端進行了阻抗匹配,因此在該模型中認為ADC的輸入阻抗等于源電阻。

圖1:ADC采樣模型

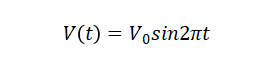

設輸入信號功率為AD的滿量程輸入功率,則該電壓表達式為:

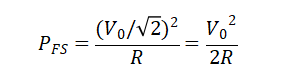

該正弦波信號的滿量程功率為:

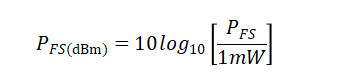

將其表示為dBm:

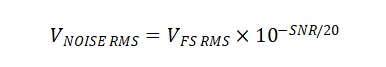

利用ADC的SNR值計算等效輸入均方根電壓噪聲(該SNR值不包括基波信號的諧波):

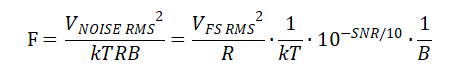

上式是在整個奈奎斯特帶寬(DC至fs/2)測得的總有效輸入均方根噪聲電壓,注意該噪聲包括源電阻的噪聲。由此得到噪聲因數F的表達式:

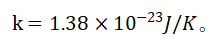

其中,SNR的單位是dB,B的單位是Hz,T=300K,

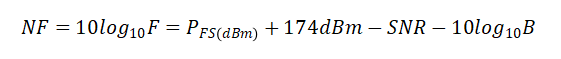

將F轉化為dB并簡化可獲得噪聲系數:

溫馨提示:明德揚擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 前端模擬采集、射頻、電荷靈敏前置放大器

有相關需求可以聯系:蘭老師18011939283(微信同號)

本文TAG:ADC噪聲系數,高速ADDA板卡,高速數據采集板卡,ADC板卡定制開發,FPGA板卡ADC板卡