明德?lián)P(MDY)在2022年承擔(dān)了多個(gè)高速ADC研發(fā)項(xiàng)目,今天給大家分享串行ADC布局布線設(shè)計(jì)要點(diǎn)!

一、PCB布局設(shè)計(jì)注意要點(diǎn):

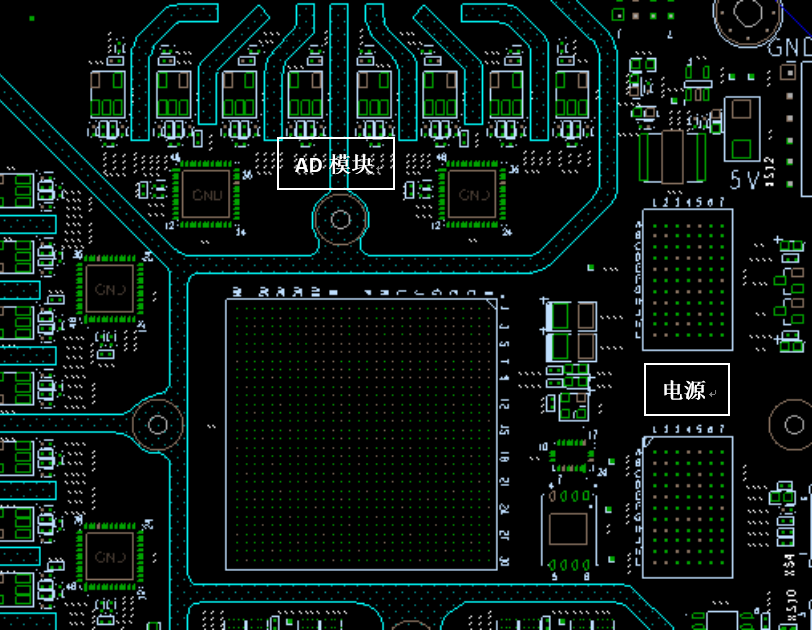

①電源部分盡量遠(yuǎn)離AD與時(shí)鐘部分。

②電源部分,主芯片F(xiàn)PGA,時(shí)鐘部分盡量放同一面,AD部分放一面,這樣既能減弱數(shù)字部分的信號(hào)對(duì)AD部分的干擾,又能方便結(jié)構(gòu)統(tǒng)一做散熱;(此設(shè)計(jì)點(diǎn)是限于板子空間小的情況下處理)。

③AD芯片與時(shí)鐘芯片的LDO電源要靠近各供給模塊芯片放置。

④AD模塊之間間距盡量大,并且AD的多路輸入端之間盡量留出空間做結(jié)構(gòu)隔離條。

二、PCB布線設(shè)計(jì)注意要點(diǎn):

①AD模塊的輸入端由單端50ohm經(jīng)過(guò)變壓器后轉(zhuǎn)為差分100ohm這段模擬信號(hào),單端阻抗要控制50ohm,差分阻抗要控制100ohm,走表層,路徑盡量短。

②AD模塊的數(shù)字部分的每1路數(shù)據(jù)信號(hào)由[AD*_D0---AD*_D*]組成,同層同組,以AD_DCO_CLK為參考進(jìn)行等長(zhǎng)匹配,等長(zhǎng)公差控制在±50mil(如空間足夠,公差可以盡量做小)。

③每個(gè)AD芯片的數(shù)字信號(hào)盡量做到等長(zhǎng),公差控制在±50mil,以保證多個(gè)AD模塊同時(shí)使用時(shí),數(shù)據(jù)信號(hào)同步。

④每個(gè)AD芯片的CLK時(shí)鐘信號(hào)到時(shí)鐘芯片的長(zhǎng)度要等長(zhǎng),走差分對(duì),控制100ohm阻抗,單對(duì)差分內(nèi)等長(zhǎng)公差控制在±5mil,差分對(duì)之間等長(zhǎng)公差控制在±10mil。

⑤ADC_SYNC信號(hào)要走T型走線,到每個(gè)AD芯片上的長(zhǎng)度要等長(zhǎng)匹配。

溫馨提示:明德?lián)P擅長(zhǎng)的項(xiàng)目主要包括的方向有以下幾個(gè)方面:

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(IMX472 IMX492)

3. PCIE采集系統(tǒng)

4. 圖像項(xiàng)目

5. 高速多通道ADDA系統(tǒng)

6. 基于FPGA板卡研發(fā)

7. 前端模擬采集、射頻、電荷靈敏前置放大器

有相關(guān)需求可以聯(lián)系:蘭老師18011939283(微信同號(hào))