本文為明德?lián)P原創(chuàng)文章,轉(zhuǎn)載請(qǐng)注明出處!作者:Vito

明德?lián)P核心板試用體驗(yàn)——第二篇

第二周的試用計(jì)劃是實(shí)現(xiàn)常見低速協(xié)議(UART,I2C,SPI)的FPGA工程,記錄自己實(shí)現(xiàn)的過程,包括協(xié)議基本理解,實(shí)現(xiàn)思路,仿真調(diào)試,上板驗(yàn)證4個(gè)流程。雖然低速協(xié)議相對(duì)簡(jiǎn)單,但是每次自己動(dòng)手寫又會(huì)發(fā)現(xiàn)之前沒有注意到的問題,又能從中鞏固自己的邏輯思維;這些看似簡(jiǎn)單的低速協(xié)議是后續(xù)所有高速接口協(xié)議的基礎(chǔ),只有基礎(chǔ)牢靠,在后續(xù)的進(jìn)階應(yīng)用中才會(huì)游刃有余。特別是對(duì)于我這樣的FPGA新人來說,基礎(chǔ)是重中之重。

下面開始介紹我的低速協(xié)議的實(shí)現(xiàn)情況。

協(xié)議理解

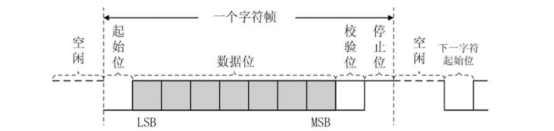

UART真的算是最經(jīng)典的通信協(xié)議之一了吧,特別是在產(chǎn)品設(shè)計(jì)調(diào)試階段,串口幾乎成了一個(gè)必備的功能。硬件信號(hào)簡(jiǎn)單,2根信號(hào)線(TX,RX),當(dāng)然不同設(shè)備連接時(shí)還需要一根共地線;3根線就能實(shí)現(xiàn)數(shù)據(jù)傳輸了。協(xié)議數(shù)據(jù)格式如下圖所示

數(shù)據(jù)收發(fā)過程分為:空閑,起始位,數(shù)據(jù)位,校驗(yàn)位(可選),停止位。對(duì)于異步的設(shè)備來說,怎樣知道每一位傳輸?shù)臅r(shí)間寬度呢?這是通過波特率來指定的。事先雙方先約定好傳輸?shù)牟ㄌ芈适嵌嗌倬涂梢粤耍?dāng)然除了波特率,一般數(shù)據(jù)位長(zhǎng)度,奇偶校驗(yàn),停止位長(zhǎng)度都是要2方確定好,不然就無法正確通信了。

實(shí)現(xiàn)思路

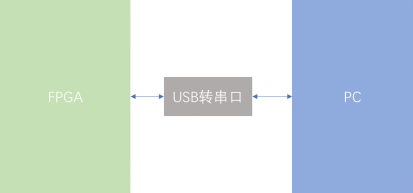

本次實(shí)現(xiàn)FPGA和上位機(jī)通信的串口工程,連接如下圖所示;具體功能是利用PC的串口工具向usb轉(zhuǎn)串口模塊發(fā)送隨機(jī)數(shù)據(jù),F(xiàn)PGA通過接收usb轉(zhuǎn)串口模塊的數(shù)據(jù)并進(jìn)行解析,并將解析的串口數(shù)據(jù)發(fā)回usb轉(zhuǎn)串口;通過查看PC上的接收數(shù)據(jù)和發(fā)送數(shù)據(jù)是否一致。

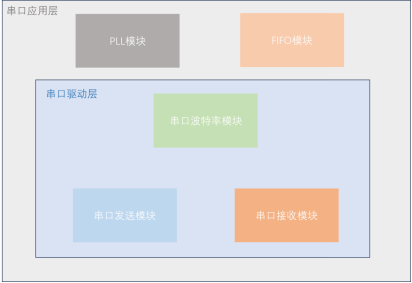

根據(jù)上述功能需求,進(jìn)行模塊劃分設(shè)計(jì),如下圖所示

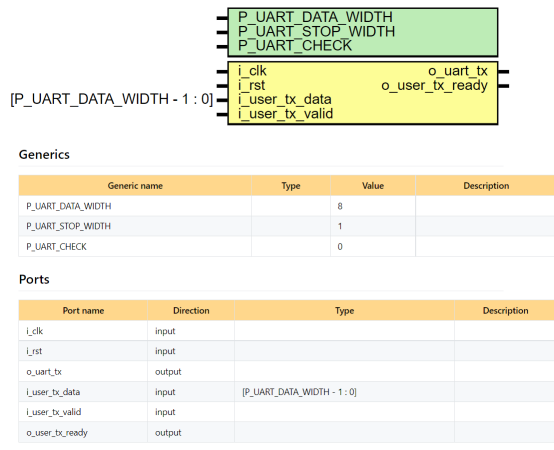

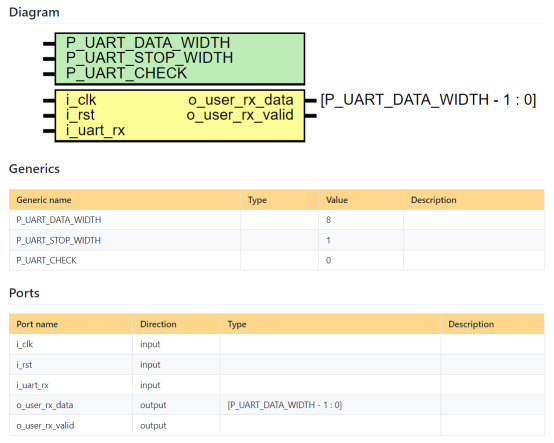

根據(jù)模塊劃分,下面就需要明確模塊的接口信號(hào),這里為了舉例就只列出tx和rx的接口信息。這里總結(jié)一下接口信號(hào)的思路:時(shí)鐘復(fù)位以及tx/rx信號(hào)就不說了,這里還加了握手信號(hào),增加每一幀數(shù)據(jù)收發(fā)的可靠性,在處理一幀數(shù)據(jù)時(shí)不會(huì)被下一幀數(shù)據(jù)到來中斷而導(dǎo)致混亂。

信號(hào)接口設(shè)計(jì)完成之后就是每個(gè)模塊代碼的編寫了,這里我就簡(jiǎn)單總結(jié)一下tx和rx設(shè)計(jì)思路。對(duì)于發(fā)送模塊:握手邏輯如果收到應(yīng)用層一幀數(shù)據(jù)的有效信號(hào),拉低ready信號(hào),同時(shí)拉高發(fā)送數(shù)據(jù)的標(biāo)志位。當(dāng)發(fā)送標(biāo)志位置1,發(fā)送計(jì)數(shù)器開始計(jì)數(shù)一幀數(shù)據(jù)的個(gè)數(shù),直到一幀數(shù)據(jù)的周期數(shù)記完并清零,表示一幀數(shù)據(jù)發(fā)送完成;于此同時(shí),tx信號(hào)根據(jù)發(fā)送計(jì)數(shù)器值依次將應(yīng)用層的并行數(shù)據(jù)移位送出。對(duì)于接收模塊:當(dāng)檢測(cè)到rx信號(hào)的下降沿之后,接收計(jì)數(shù)器開始計(jì)數(shù),計(jì)數(shù)值為一幀數(shù)據(jù)的周期長(zhǎng)度;并根據(jù)計(jì)數(shù)值移位采樣rx數(shù)據(jù),轉(zhuǎn)化成并行數(shù)據(jù),并拉高valid有效信號(hào),表示一幀數(shù)據(jù)的接收過程。

仿真調(diào)試

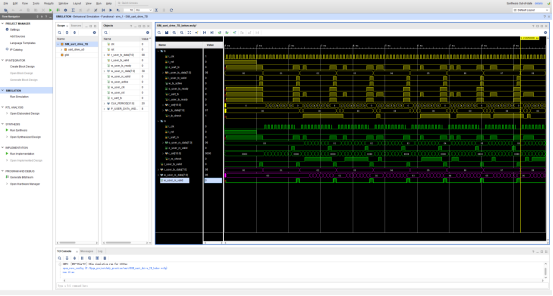

編寫完串口驅(qū)動(dòng)模塊之后,需要進(jìn)行仿真調(diào)試,下面是仿真波形。

仿真激勵(lì)中,發(fā)送數(shù)據(jù)給的是1,2,3……255 數(shù)據(jù),可以看到圖中紫色部分為收發(fā)數(shù)據(jù)的波形,可以看到收發(fā)數(shù)據(jù)一致,因此仿真調(diào)試ok。

上板驗(yàn)證

在實(shí)際應(yīng)用中,需要考慮更多的非理想環(huán)境。1.罪魁禍?zhǔn)拙褪钱惒綍r(shí)鐘問題,運(yùn)行時(shí)間越長(zhǎng),所累積的時(shí)鐘誤差就會(huì)越來越大;所以很可能運(yùn)行一段時(shí)間就會(huì)出現(xiàn)錯(cuò)誤數(shù)據(jù),因此需要加上時(shí)鐘矯正減少時(shí)鐘累積誤差,解決辦法就是用高頻時(shí)鐘采集rx信號(hào),當(dāng)檢測(cè)到一次數(shù)傳輸時(shí)再打開串口接收時(shí)鐘,當(dāng)發(fā)送完成之后再將串口接收時(shí)鐘關(guān)閉從而解決累積偏差。2.收發(fā)數(shù)據(jù)時(shí)有時(shí)一幀數(shù)據(jù)還沒有處理完成,可是下一幀數(shù)據(jù)已經(jīng)到來,如果不緩存就會(huì)出現(xiàn)丟幀的問題,因此在應(yīng)用層增加了一個(gè)fifo,用于緩存來不及處理的數(shù)據(jù)。

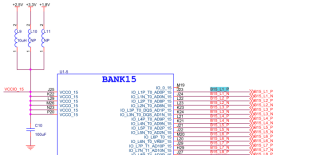

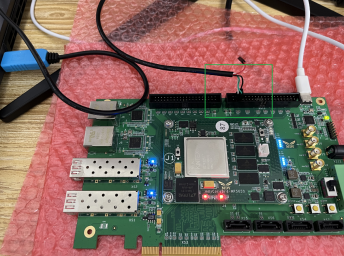

我之前看原理圖底板上是有FT232usb轉(zhuǎn)串行的芯片的,但是好像只連接了JTAG接口,電腦并沒有識(shí)別到串口號(hào),所以我只能在擴(kuò)展口找2個(gè)IO了。翻遍了原理圖和手冊(cè)都沒有找到一個(gè)XS11的引腳對(duì)應(yīng)關(guān)系,沒辦法只能先通過原理圖猜測(cè)信號(hào)所對(duì)應(yīng)的實(shí)際引腳位置,好在我手邊有萬用表,然后通過測(cè)量知道了實(shí)際對(duì)應(yīng)位置,希望之后將一些接口的實(shí)際信號(hào)做一個(gè)圖示,自己找信號(hào)位置太麻煩了。。。這里我挑了2個(gè)IO:J23/J24作為uart的tx 和 rx,連接一個(gè)usb轉(zhuǎn)串口模塊,然后連接電腦,實(shí)際連接如下圖所示。

下載bitstream之后,打開電腦串口軟件,定時(shí)一直發(fā)送數(shù)據(jù),觀察收發(fā)數(shù)據(jù)是否一致,測(cè)試結(jié)果如下圖所示。

可以看到,經(jīng)過一段時(shí)間的連續(xù)運(yùn)行,收發(fā)數(shù)據(jù)量一致,且結(jié)果正確。因此該串口工程上板成功。

眾所周知,XILINX-Kintex系列以性價(jià)比著稱,在高性能低功耗的前提下,價(jià)格也相對(duì)較低,目前市場(chǎng)上不存在缺貨的情況,所以當(dāng)使用量大的時(shí)候,價(jià)格也會(huì)更有優(yōu)勢(shì)。所以在研發(fā)工作中,這個(gè)款核心板是非常適用于二次開發(fā)和產(chǎn)品使用的。

明德?lián)P推出0元試用核心板活動(dòng)正在進(jìn)行中,可以聯(lián)系客服黃老師參加:13316124179(微信同號(hào))

如需直接購買可點(diǎn)擊淘寶鏈接:請(qǐng)點(diǎn)擊