如果同學們的學習問題我們帖子里面沒有的,請第一時間聯系我微信同步:易老師13112063618

明德揚還做了抖音系列短視頻,感興趣可以關注明德揚抖音號:FPGA技巧分享(87481069842)內容不斷更新!點贊+關注,學習不迷路!

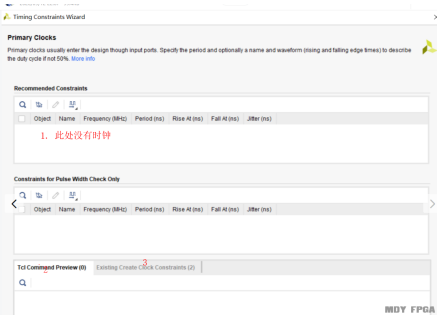

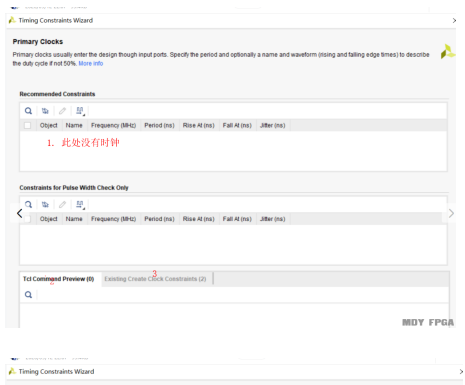

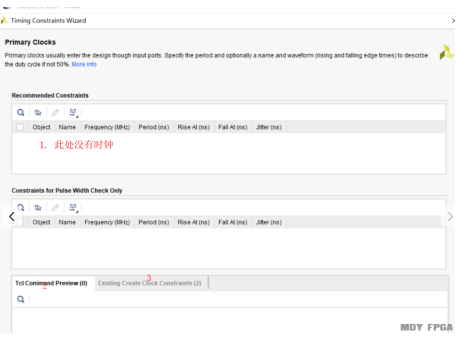

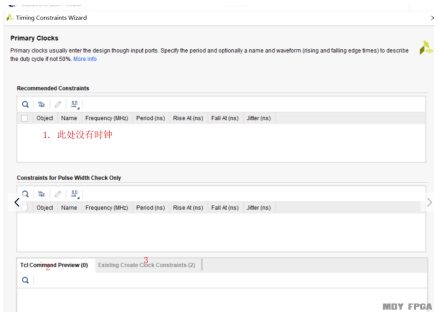

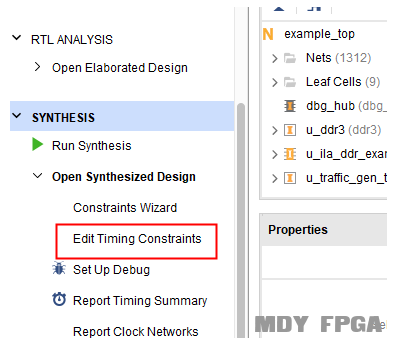

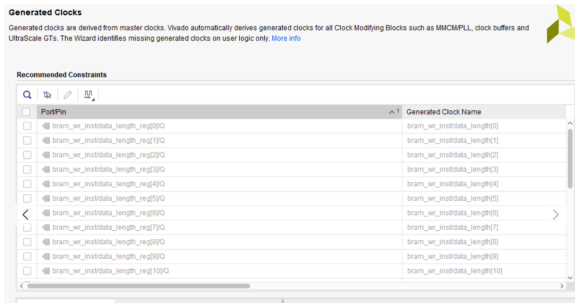

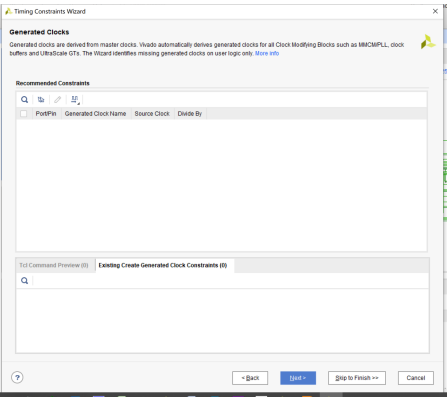

【問題1】 VIVADO的時鐘約束向導,常無法找到時鐘,如下圖所示,位置1中應該要識別出時鐘。

答:請注意,位置1的地方是列出的是“沒有被約束的時鐘”,如果該時鐘已經被約束了,就不會在這里列出來了。

注意上圖中3的位置,該列說明了有2條時鐘約束。可以點擊這里看看,是不是已經對時鐘進行約束了。為什么會有時鐘被約束了呢?因為該工程已經有約束文件。

【問題2】VIVADO/QUARTUS練習中,rst_n是否需要約束?

答:一個完整的約束,其基本要求是:所有的路徑都覆蓋,包括所有的輸入管腳和輸出管腳。所以,rst_n需要約束。注意的是,該信號是輸入信號,但沒有隨路時鐘進來。所以該信號可以認為是無時鐘的情形,按照課程理論,應該定義一個虛擬時鐘。定義了虛擬時鐘后,再重新使用約束向導,約束rst_n。

【問題3】在VIVADO中,如何設置虛擬時鐘?

答:虛擬時鐘不能在時序約束向導中添加,需要在下面窗口添加

在Edit Timing Constraints中點擊,然后在creat clock窗口中,雙擊“Double click to create a Create Clock Constrtaint”。在彈出的窗口中

Clock name為該時鐘命一個名字,Source objects是不需要填的,因為是虛擬時鐘,就是沒對象了。

【問題4】時序約束出現時序違例(Slack為負數),如何處理?

答:首先指出一個誤區:當約束出現錯誤時,想當然地認為是“時序約束做得不對”,所以應該怎么去改“時序約束”,從而讓這些錯誤消失,這是一個錯誤的觀念。

時序約束的作用:在于檢查“設計是否滿足時序要求”,它是用來審視自己設計的,很多情況是,要改設計代碼來滿足時序要求。

當時序約束提示有錯誤時,應該閱讀“時序報告”,從報告中分析時序路徑(數據到達時間、時鐘到達時間和數據要求時間等),根據報告分析錯誤的原因,并根據原因來實行不同的方法。以建立時間違例,說明具體方法如下

1. 時序報告中,找到提示錯誤的路徑,即目的寄存器,以及源寄存器。注意,這是兩個寄存器的點。

2. 首先判斷,源寄存器的時鐘,與目的寄存器的時鐘,是否相同。如果不同,可以認為是異步時序,見步驟3;如果是相同,則看步驟4。

3. 如果是異步電路,那么處理方法如下:

A. 確認做了異步處理。對于數據,則是通過異步FIFO來做異步處理;如果是控制信號,則要經過打兩拍來處理。

B. 確認做了異步處理后,仍然會報“時序違例”的。這個時候,可以該路徑設置成set false path,不用再檢查。

4. 同步電路下,具體處理如下:

A. 查看兩個寄存器點之間,經過了多少加法器、乘法器、除法器等。

B. 對于除法器,要特別留意,一般是1個時鐘計算不完的。那么可以 a.想辦法不用除法;b. 通過使能信號控制獲取除法器結果的時間。

C. 對于乘法器和加法器,或者其他組合電路較多的。想辦法分隔成流水線來實現。可以參考MDY 流水線的內容。

5. 如果是IP核的違例,檢查是否時鐘不滿足IP核的要求。如果沒問題,就不用管。

6. 如果是ILA等在線調試工具路線的違例,則一般不用處理。

7. 如果是線延時太長的,可以嘗試打一拍處理。即A->B的線太長,可以打一拍,變成A->C->B,這樣線延時就小了。

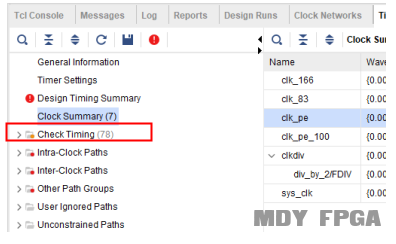

【問題5】VIVADO中,如何查詢未約束的時鐘、未約束的輸入延時和輸出延時等?

答:如下圖,在VIVADO的時序約束界面中,在下面欄目可顯示未約束的地方。

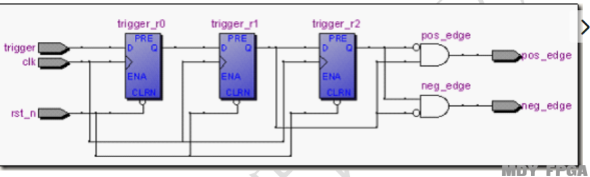

【問題6】如下圖所示,跨時鐘域打兩拍的方法,其實只是一個信號的傳遞,當第一個信號出現不穩之后或者錯誤之后,后面就會把這個錯誤的信號繼續傳遞下去,并沒有起到糾錯的作用

答:上圖中打兩拍的方法,其本質不是為了“糾錯”,它的作用是為了防止“亞穩態”。

防止亞穩態的本質:防止中間狀態過長。之所以采用兩級觸發器的方法,是因為D觸發器出現亞穩態的可能性非常小,而兩級D觸發器出現亞穩態的概率就更小了。

【問題7】既然打兩拍的方法不能糾錯,那“打兩拍”還有什么意義?

答:錯誤有很多種,有些錯誤是1次性錯誤,而有些是系統性錯誤。

傳輸過程中,如果發了0,如果全部接收模塊都認為是1,這并不是問題,這是可以預防和可控的(例如檢測多幾次就行了)。

但是亞穩態的時候,如果發了0,但部分接收認為認為是1,而另一部分模塊認為是0,至于哪些模塊認為是1哪些是0,這是隨機的,不可預知的,這就是災難。更詳細的內容,建議參考:FPGA知識大串講:http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=581

【問題8】模塊A的時鐘clka為100MHz,模塊B的時鐘clkb為300MHz。現在模塊A要把32bit的數據送給模塊B。模塊A要如何發送,模塊B要如何接收呢?

答:

方法1:采用異步FIFO的方法。

方法2:采用指令信號的方法傳輸,模塊A產生vld信號給模塊B,模塊B對vld進行同步化處理(打兩拍)后,檢測同步化信號的上升沿。需要注意的,VLD的信號是讓模塊B周期的三倍或以上。由于clka是100M,產生的vld是10ns,而clkb是300M,周期是3.33ns。所以模塊A只要產生1個時鐘的vld給模塊B即可。

【問題9】模塊A的時鐘clka為300MHz,模塊B的時鐘clkb為100MHz。現在模塊A要把32bit的數據送給模塊B。模塊A要如何發送,模塊B要如何接收呢?

答:

方法1:采用異步FIFO的方法。

方法2:采用指令信號的方法傳輸,模塊A產生vld信號給模塊B,模塊B對vld進行同步化處理(打兩拍)后,檢測同步化信號的上升沿。需要注意的,VLD的信號是讓模塊B周期的三倍或以上。由于clka是300M,產生的vld是3.33ns,而clkb是100M,周期是10ns。所以模塊A要產生10個時鐘的vld給模塊B。

【問題10】一塊電路板上,有兩個芯片,芯片A的時鐘clka為100MHz,芯片B的時鐘clkb為100MHz。現在芯片A要把32bit的數據送給芯片B。模塊A要如何發送,模塊B要如何接收呢?

答:

方法1:采用異步FIFO的方法。

方法2:采用指令信號的方法傳輸,模塊A產生vld信號給模塊B,模塊B對vld進行同步化處理(打兩拍)后,檢測同步化信號的上升沿。需要注意的,VLD的信號是讓模塊B周期的三倍或以上。雖然clka和clkb都是100M,但他們不是同一個晶振產生的,因此都是異步時鐘。為了滿足以上要求,所以模塊A要產生3個時鐘的vld給模塊B。

【問題11】A, B時鐘都是50M,但是他們不相關,為了防止編譯器把他們默認為同一個時鐘,是不是要用一個異步時鐘組約束,來告訴編譯器他們是不同的兩個時鐘?

答:一般分別產生A和B的時鐘約束即可。

【問題12】 建立時間可以是負值嗎?

答:建立時間當然可以是負數了。負數表示,可以在時鐘上升沿后數據才變化。(建立時間是器件的屬性,至于怎么器件怎么做到的,那就要問器件工程師了)

【問題13】 程序原本時序可以通過,加上singalTap節點之后時序不通過是什么原因?

答:增加signaltap ILA等在線調試工具時,需要使用到內部的資源,例如RAM、選擇器、寄存器等,增加后再去綜合和布局布線。由于改變了資源,因此肯定對時序是有影響的,有可能改善了也有可能惡化了。如果時序有問題,分析路徑,如果是在線調試工具路徑,評估是否會有風險,沒風險就算了

【問題14】時序約束什么時候要做?

答:

1.在需要的時鐘頻率下,如果邏輯功能不穩定,那么就需要時序約束。

2.一般時鐘大于100M的時候,我們就要做一下時序約束。

【問題15】時序約束建立時間和保持時間的生活案例。

答:可以想象,有一個人從家里出發去機場,搭乘13點的飛機。

1. 13點起飛,起飛前15分鐘要到機場,這個15分鐘,就類似于建立時間要求。

2. 機場每小時有要飛一趟飛機,每個小時表示的是時鐘周期。

3. 飛機起飛后,機場要保持10分鐘,之后才能來下一批乘客,這個10分鐘就是保持時間。

4. 這個人出發去搭13點的飛機,因此他要在12點45分之前到機場,并且是12點10分之后到機場。既不能早到,也不能晚到機場。

5. 如果這個人12點45分之后才到機場,那就搭不上本趟飛機,即違反了建立時間要求。(建立時間影響的是自己坐飛機)

6. 如果這個人12點10分前就到了機場,那就會因此上一趟飛機的起飛,即違反了保持時間要求。(保持時間不滿足,影響的是上一批乘客坐飛機)

7. 這個人是計劃去機場,因此他要估算幾點能到機場。首先他會算所有情況下的最大延遲,如剛到路口紅燈就來了、走路最慢等,在這種最慢的情況下,如果能在12點45分前到,說明建立時間沒問題。然后,他會算所有情況下的最小延遲,如剛到路口綠燈,走路最快,在這種最快的情況下,如果能在12點10分后才,那說明保持時間沒問題。

【問題16】為什么建立時間分析的時鐘到達時間要加一個時鐘周期而保持時間分析則不用呢?

答:因為建立時間是源寄存器發出數據,目的寄存器采集,也就是上一個時鐘發出來,本時鐘采集。這里有一個時鐘周期的因素,所以要加1個時鐘周期。而保持時間分析,則是“本個時鐘”發出數據后,如果延時太小,會影響“本個時鐘”對上一個數據的采集,因為不需要加1個時鐘周期。另外,要注意一點,保持時間是跟時鐘周期無關的。

【問題17】一個外部的信號,經過狀態機的“組合邏輯”,這也要做同步處理嗎?

答:需要做同步處理的。首先明白一點,FPGA里的時序邏輯=組合邏輯 + D觸發器。組合邏輯的最終結果,還是要發D觸發器的。所以還要做同步化處理的。

【問題18】請教下,做時序約束,做到這步時,這些都要勾選上嗎?

答:當然不是,要逐個分析確認,沒有一選就全選上的道理。

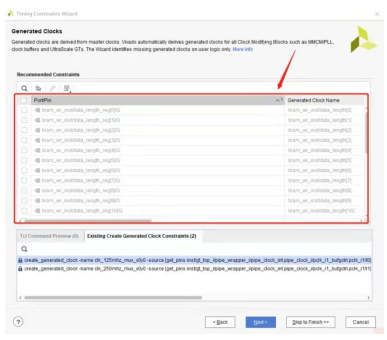

【問題19】下面的生成時鐘約束,是否一定要勾選?

答:這應該看生成時鐘那一節視頻,里面重點強調了“什么叫時鐘”? 上面的圖里,您應該要搞清楚,它被識別出時鐘了,正不正常?如果是正常,那您肯定是要添加約束,定義頻率吧。如果它不應該識別出時鐘了,那您應該檢查您的代碼,看是不是代碼不規范引起,或者有沒有潛在的問題。注意一下:約束不是目的,約束是為了查看報告,看設計有沒有問題的。

【問題20】系統同步只可能是單沿采集?沒法像DDR那樣雙沿采集?

答:系統同步也是可以是雙沿采集的,但比較少。課程里,只是介紹了部分情形。如果想看所有情形有哪些,可以打開VIVADO的時序約束向導,可以設置INPUT DELAY窗口查看。

【問題21】QUARTUS生成SDC時,默認出現的那條時鐘約束是正常的么?我自己刪掉就行了?

答:默認生成的當然是不正常。

【問題22】老師問一下,我畫的后邊那個部分,我認為應該沒有數據吧?

答:不是 這個不是有沒有數據的概念 而是數據是否穩定的概念。

【問題23】請問下有沒有針對SDC時序約束語法的講解嗎?

答:時序約束里,只講解了用到的部分。如果想看更多部分,我估計你要看這個語法的權威資料了。

【問題24】老師您好,我在學習時序約束視頻,看到第一個視頻這塊“流水線設計思路:乘法器可以分成加法器,然后加法器還可以分成什么,一直聽不清”

答:最后可以分成與門這些最簡單的門電路。

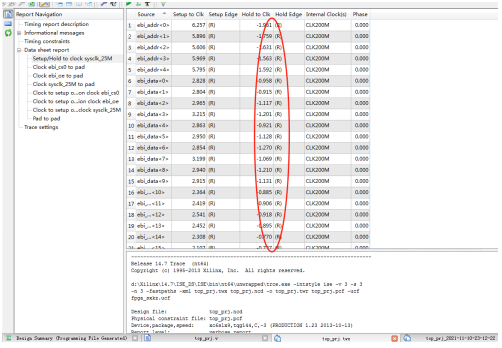

【問題25】老師請問紅色的是不是不滿足時序要求?

答:不是的,setup和hold時間形成一個時間窗,只要在這個時間窗里信號穩定就餓可以了 在使用時序分析工具的時候,字體為紅色時間提示是不滿足時序要求

【問題26】什么樣的信號會被工具判斷為時鐘?

答:一個信號被VIVADO QUARTUS判斷為時鐘,不是看名稱里是否帶有“clk”等字母。而是主要看其是否用于“時鐘”的行為中,主要有如下幾種情況。

1. 被關聯到always敏感列表里的時鐘信號。說明會被連到觸發器的時鐘端,所以會被認為為時鐘。

2. 被連到PLL和MMCM等時鐘管理器的輸入端,這會被認為是時鐘。

3. 被連到鎖存器的條件端,例如一個沒有補全的組合邏輯代碼,其條件就會被認為時鐘。

【問題27】用ila抓取信號分析,發現異常,而時序約束報告正常,因此可以認為時序報告正常,而時序會有問題?

答:

1.在線邏輯分析儀是用于判斷邏輯是否出現問題,可以認為是檢查時鐘節拍下的邏輯判斷。而時序約束是解決D觸發器的建立時間和保持時間問題,是一個時鐘內的時序問題。

所以,不能用ila來推導時序約束,這是不同層次的問題。

2.官方可以保證,用戶代碼和時序約束的生成結果是正確,即在輸入的代碼和約束,給出來的報告一定是正確的。但時序約束對不對,這是客戶保證的。

3.出現結果不對,可能性很多,不一定是時序問題,要注意“充分必要條件”。

【問題28】同樣的工程不做任何改動,有時編譯后下板驗證正確,有時編譯后下板驗證不正確,是不是時序問題呢?

答:有可能是,但又不一定是。這是時序不滿足的一種現象。但反過來,沒有說,出現這種現象,就一定是時序問題。

【問題29】設置時鐘約束時,假如有虛擬時鐘的情況,虛擬時鐘是必須要設置的嗎?

答:

1.原則上所有接口有應有約束。

2.設置虛擬時鐘,可以方便將對應信號歸到該虛擬時鐘好,這樣方便做分析,例如看有沒有跨時鐘域等。

3.是不是一定要做,取決于項目老大要求,不做不一定有問題。

【問題30】一個always模塊下,if 、else if,,,else ,寫的太多了 ,是不是會容易造成時序問題呢?這種說法對嗎?

答:這里有一個定義要搞清楚的,什么叫“多”?

1.是3個就多,還是10個?每個人標準不同。

2.即使是同一個人,使用不同的器件,這個“多”也是不同的。有些高級的器件,10個IF也不多,有些低端器件,3個也多。

3.即使同一個人,同一個器件,但if里的判斷條件也有講究。如果判斷條件里一個除法器,那1個if也多,如果只是判斷0和1,那么10個也算少。

4.最具可操作性的做法,給定時鐘約束,看時序報告。報告沒問題,那就是沒問題;否則會有時序違例的錯誤。

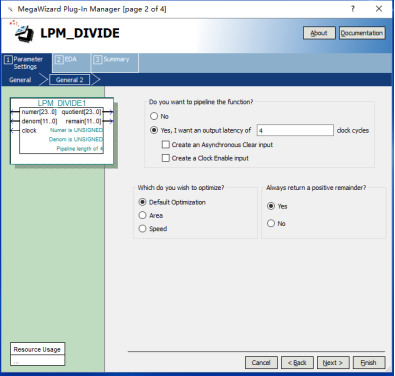

【問題31】output latency一般設置成多少呢?pipeline 有啥用?

答:由于除法器占用資源較大,難以在一個時鐘周期內計算完畢,需要多個時鐘才計算完,這個pipeline就是設置多少個時鐘周期的。

如果您不清楚要多少個,設置填一個較大的數,然后看時序報告是否正確。如果正確,就沒問題。

【問題32】請問:MDY的案例中,為什么串口需要對din進行同步化,而SCCB就不需要對sio_din進行同步化?sio_din也是外部器件進來的嗎?

答: 是否要對信號進行同步化,最核心的理解是“該信號是否能夠保證滿足建立時間和保持時間要求”,也就是“該信號的變化和時鐘存在確定性相位關系”。

以串口為例,串口的輸入信號與FPGA時鐘是沒有任何聯系的,該輸入信號可以在任意時刻變化,也就有可能剛好在時鐘上升沿變化,從而不滿足建立時間要求,

因此要做同步化處理。而SCCB案例中,由FPGA時鐘里產生了sio_dout、SCK等信號,而sio_din在sck作用下變化,所以sio_din與FPGA時鐘是有一定關系的。

可以認真看時序圖,在FPGA對sio_din有采樣時刻,時序已經要求sio_din要穩定不變的,所以可以不用做同化處理。

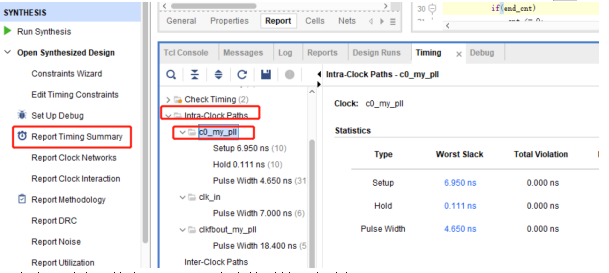

【問題33】請問工程中使用了PLL,在做時序約束時,generate clocks窗口顯示沒有PLL產生的時鐘,如下圖,為什么?

答:PLL、MMCM等產生的時鐘,默認是由工具自動推導約束的,不用用戶來約束。雖然用戶沒有約束,事實上是做了分析的。例如下圖中,可以看到c0_my_pll這個時鐘。其中,c0_my_pll是工具自動命名的。

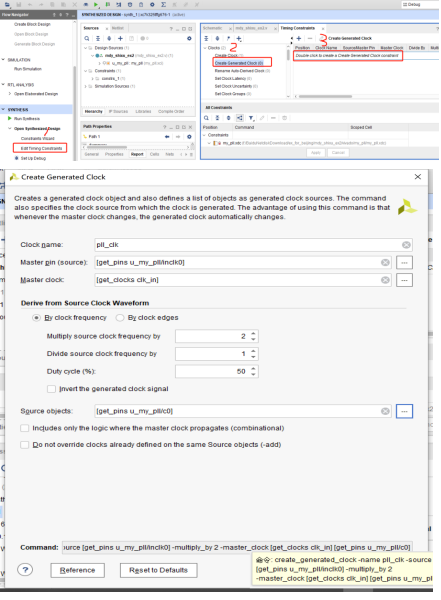

用戶也可以自己約束PLL/MMCM產生的時鐘,方法如下圖。

按照方面方法,約束好,重新分析就可以了。

【問題34】問:如果使用的IP核內部代碼出現了時序約束違例,該如何解決?

答:IP核是由官方提供的代碼,一般用戶不能修改,如果該IP核出現違例,可以從以下方向入手:

1. 一般IP核是有指定的頻率范圍,可以從數據手冊找到,請看是否滿足了數據手冊要求。

2. 如果頻率正確,還會出現報錯,可以檢查時鐘和復位管腳有沒有正確使用,根據經驗,這通常是引起問題的原因。

3. 嘗試修改編譯策略,重新綜合看看。

【問題35】問:請問時序約束只是針對FPGA輸入與輸出端進行約束,而不是針對FPGA內部模塊之間或者模塊里面。這樣理解是否正確?

答:不是的,內部肯定也跟約束有關。

【問題36】問:老師,想問下時序約束,DDR4的uiclk需要時鐘約束嗎?

答:需要的,設置好時鐘頻率,周期就可以了,就是需要create clock就好了

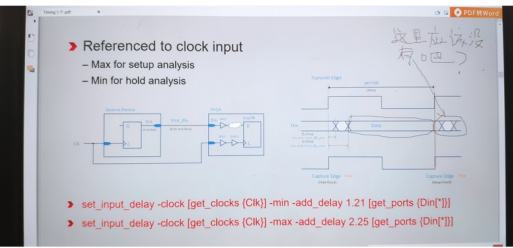

【問題37】問:關于input delay的抖動解釋。

答:需要理解的抖動,不是指一個波形的結果,是多個波形疊加的結果。假設說一個PWM波形,周期為10ns,理想情況下變高為2.5ns,變低在7.5ns。由于存在不確定延時情況,所以有時候變高在2.6ns,變低在7.6ns。有時候變高在2.4ns,變低在7.4ns。有時變高在2.3ns,變低在7.3ns。數個波形疊加,就看到了抖動的現象。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)