如果同學們的學習問題我們帖子里面沒有的,請第一時間聯系我微信同步:易老師13112063618

明德揚還做了抖音系列短視頻,感興趣可以關注明德揚抖音號:FPGA技巧分享(87481069842)內容不斷更新!點贊+關注,學習不迷路!

【問題1】關于FIFO的深度計算問題,可以看此貼:

答:http://www.cqqtmy.cn/jishuwenz/2020/0219/914.html 此答案來自于明德揚的書籍《手把手教你學FPGA》,電子版可以在此貼下載:http://www.cqqtmy.cn/wentijieda/20210410/1324.html

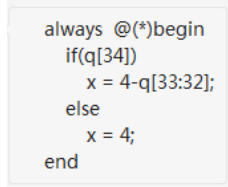

【問題2】圖中X代表什么意思

答:這個X是表示并串轉換的次數。FIFO輸出的Q是32位,正常情況下,是有4個字節的有效數據,因此x=4。但有一個情況,在包文的最后一個數據時,有可能是只有1字節、或者2字節、或3字節,或4字節有效,這個有效多少是取決于mdy的值(經過FIFO后,即是Q的33和32位)。可以代入數據可以看到x的值。例如:當q[33:32]=1時,表示有1字節無效,即3個字節有效,所以此時x等于3。

【問題3】問:FIFO仿真時,與預想的不一樣,有時候會出讀出的不對?

答:在做FIFO仿真的時候,如果出現仿真出錯的情況,建議按如下方式定位。

1. 一定要抓取FIFO的內部信號來觀察。注意,一定是內部信號,例如FIFO這個模塊的q、rdreq等。

2. 要先確認FIFO的輸入端,即wrreq信號和寫數據,一個時鐘(寫時鐘)一個時鐘去對,最好記錄一下這個數據。

3. 其次,確認FIFO的輸出端,即讀時鐘、rdreq和q這三個信號,一個時鐘一個時鐘去對,把數據記錄下來。

4. 最后,再用寫數據和讀數據進行對比。

另外,一般是不會有問題的,請認真核對。請注意,有部分同學反饋還是出錯,我們技術經過遠程定位后,發現同學在確認數據時,沒有按時鐘一個一個來數,導致了疏忽和遺漏,請確保一定要仔細核對。

【問題4】wrusedw是寫側保持數據個數, rdusedw是指讀出讀出了多個數據個數?

答:無論wrusedw還是rdusedw,均表示FIFO內保存有多少個數據。它們之間的區別僅僅是時鐘域不同,wrusedw對應的寫時鐘域,即與寫時鐘對齊的信號;rdusedw對應的是讀時鐘域,即與讀時鐘對應的信號。由于寫時鐘和讀時鐘頻率、相位等不同,所以wrusedw和rdusedw是無法完成一致的,使用時要注意。

溫馨提示:明德揚2023推出了全新課程——邏輯設計基本功修煉課,降低學習FPGA門檻的同時,增加了學習的趣味性,并組織了考試贏積分活動

http://www.cqqtmy.cn/ffkc/415.html

(點擊→了解課程詳情?)感興趣請聯系易老師:13112063618(微信同步)

明德揚除了培訓學習還有項目承接業務,擅長的項目主要包括的方向有以下幾個方面:

1. MIPI視頻拼接

2. SLVS-EC轉MIPI接口(IMX472 IMX492)

3. PCIE采集系統

4. 圖像項目

5. 高速多通道ADDA系統

6. 基于FPGA板卡研發

7. 多通道高靈敏電荷放大器

8. 射頻前端

需要了解相關信息可以聯系:易老師13112063618(微信同號)