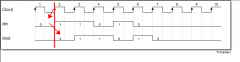

本文設計思想采用明德揚至簡設計法。在使用FPGA設計系統時,常需要利用FIFO進行數據緩存保證數據不丟失,因此計算FIFO深度是至關重要的。FIFO的深度主要取決于“最惡劣”的情況,以下對于兩種最常見的場合進行分析。

一.已知讀寫兩側帶寬及最惡劣情況,求FIFO深度

如:

分析:

計算:

Nwr = 120

Nrd = t/Trd = 120*Twr/Trd = 120*frd/fwr = 120*80/100 = 96

x = Nwr - Nrd = 120 - 96 = 24.

由于FIFO深度只能取2的整數次冪,因此最小深度為2^5 = 32.

二.為保證數據連續輸出,求讀取前FIFO內至少緩存數據量

如:

分析:

計算:

Nrd = 8192

Nwr = t/Twr = 8192*Trd/Twr = 8192*fwr/frd = 8192*80/100 = 6553.6B

發送水線x滿足 Nwr +x = 8192 --> x = 8192 - Nwr = 1638.4B

FIFO深度為2^11 = 2048.