本文為明德揚原創文章,轉載請注明出處!

SDRAM即同步動態隨機存儲單元,主要用來存儲較大容量的數據。我們都知道,數據在處理的過程中一般都需要進行存儲,開發板上常見的存儲方式有FPGA內部芯片RAM資源、外部Flash存儲器和外部SDRAM存儲器。除了Flash,其他兩種存儲器都是掉電即丟失數據,由于Flash掉電能夠保持內部數據,因此Flash主要用來固化程序或者固化參數。FPGA片內的RAM資源稀少而且珍貴,在大容量存儲場合如圖像數據緩存時,只能選擇外部存儲如SDRAM、DDR3等存儲器。在MP801開發板上就含有三塊SDRAM芯片,可以滿足較大數據的高速讀取。作為新手進階過程中所面對的一個較復雜的接口,很多人對SDRAM的工作方式及接口時序不是很清楚。經過查閱數據手冊與搜集相關的技術文檔,我整理了一篇有關SDRAM接口讀寫時序的文章,希望能夠幫助不了解的同學對SDRAM數據讀寫有更進一步的認識。

一、SDRAM初始化

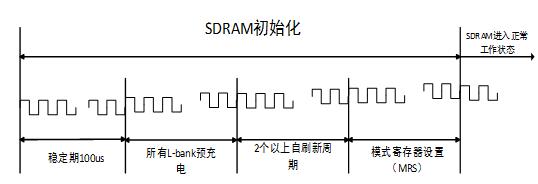

在SDRAM內部有一個邏輯控制單元,并且有一個模式寄存器為其提供控制參數。每次開機時SDRAM都要先對這個控制邏輯核心進行初始化,關鍵階段就在于模式寄存器(MR, Mode Register)的設置,簡稱MRS(MR Set)。

SDRAM必須以預定義的方式啟動和初始化。在電源同時作用于Vdd和Vddq后開始初始化SDRAM,此時的時鐘穩定并且將DQM和CKE信號拉高。在向SDRAM發命令之前需要有100us的延時,此時SDRAM不執行任何操作。在100us延時滿足后,需要對Bank進行預充電,在此期間所有的Bank處于空閑狀態。預充電之后會有至少兩個自刷新,完成自刷新便可以對SDRAM進行模式寄存器配置。

圖1 SDRAM初始化時序

SDRAM模式寄存器所控制的操作參數:地址線提供不同的0/1信號來獲得不同的參數。在設置到MR之后,就開始了進入正常的工作狀態。

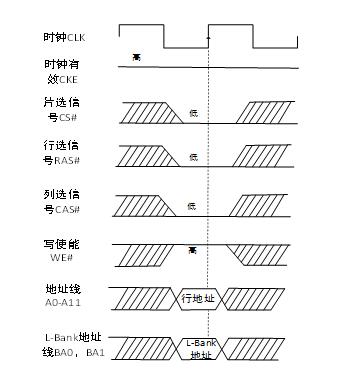

二、行激活

初始化完成后,在向SDRAM發送讀或寫命令之前必須打開該Bank中的一行,通過ACTIVE命令來確定要激活的Bank和行。要想對一個L-Bank中的陣列進行尋址,首先要確定行(Row),然后確定列。片選信號與L-Bank選擇信號與行有效同時進行。

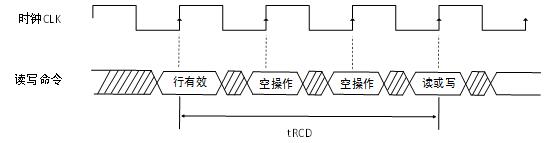

圖2 行有效時序

從上圖中可以看出,在片選信號、Bank地址選定的同時,RAS(Row Address Strobe,行地址選通脈沖)也處于有效狀態,此時An地址線發送具體的行地址。行地址位寬為12,共可以指示2^12=4096個具體的行地址。當行地址被激活后,相應的Bank也被激活,因此行激活又叫L-Bank激活。

三、列讀寫

行地址確定以后,就要對列地址進行尋址了。地址線仍使用A0-A11,即行地址與列地址共用地址線。當列地址選通后,就需要對SDRAM進行讀寫,而給SDRAM讀命令還是寫這就由WE#信號來決定。當WE#信號拉低時,SDRAM接收到的是寫命令;當WE#拉高,SDRAM接收讀命令。列尋址信號與讀寫命令是同時發出的。雖然地址線與行尋址共用,但CAS(Column Address Strobe,列地址選通脈沖)信號則可以區分開行與列尋址的不同,配合A0-A9,A11來確定具體的定址。

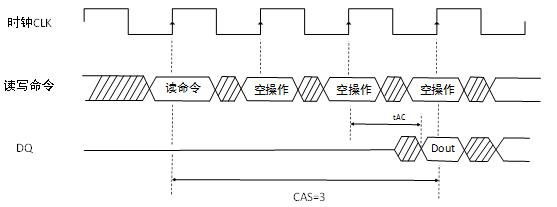

在發送列讀寫命令時必須要與行有效命令有一個時間間隔,這個時間間隔被定義為tRCD,即RAS to CAS Delay(RAS至CAS延遲)。比如tRCD=3,就代表延遲周期為3個時鐘周期,即在行有效命令發出后,經過3個時鐘周期的延時,才能發送列讀寫命令,SDRAM進入數據讀寫操作。

圖3 tRCD=3的列讀寫時序圖

四、讀操作

讀命令從輸入信號BA0、BA1中選取要進行讀數據操作的BANK,并在已激活的行中進行突發讀操作。輸入的A0-A7用來進行列尋址。在選定列地址后,就已經確定了具體的存儲單元,剩下的事情就是數據通過數據I/O通道(DQ)輸出到內存總線上了。但是在CAS (列地址選通脈沖)發出之后,仍要經過一定的時間才能有數據輸出,從CAS與讀取命令發出到第一個數據輸出的這段時間,被定義為CL(CAS Latency,CAS潛伏期)。由于CL只在讀取時出現,所以CL又被稱為讀取潛伏期(RL,ReadLatency)。CL的單位與tRCD一樣,為時鐘周期數,具體耗時由時鐘頻率決定。CAS并不是在經過CL 周期之后才送達存儲單元。實際上CAS與RAS一樣是瞬間到達的,但CAS的響應時間要更快一些。下圖展示了CAS=3時的讀時序:

圖4 CAS Latency=3的示意圖

由于存儲體中晶體管存在反應時間,從而造成數據不可能與CAS在同一上升沿觸發,因此要延后至少一個時鐘周期。考慮到芯片體積較小的因素,存儲單元中的電容容量很小,所以信號要經過放大來保證其有效的識別性,這個放大/驅動工作由S-AMP負責,一個存儲體對應一個S-AMP通道。但它要有一個準備時間才能保證信號的發送強度(事前還要進行電壓比較以進行邏輯電平的判斷),因此從數據I/O總線上有數據輸出之前的一個時鐘上升沿開始,數據即已傳向S-AMP,也就是說此時數據已經被觸發,經過一定的驅動時間最終傳向數據I/O 總線進行輸出,這段時間我們稱之為tAC(Access-Time-from-CLK,時鐘觸發后的訪問時間),單位是ns。在突發讀操作完成后,如果選擇了自動預充電模式,那么該行就會直接進入充電。如果沒有選擇此模式,那么該行將保持打開狀態,供后續訪問。自動預充電模式的選擇與A10的值有關,A10為高時為自動預充電命令模式。

五、寫操作

數據寫入的操作也是在tRCD之后進行,但此時沒有CL(CL只出現在讀取操作中),行尋址與列尋址的時序一樣致,只是在列尋址時,WE#為有效狀態。由于數據信號由控制端發出,輸入時芯片無需做任何調校,只需直接傳到數據輸入寄存器中,然后再由寫入驅動器進行對存儲電容的充電操作,因此數據可以與CAS同時發送,也就是說寫入延遲為0。不過,數據并不是即時地寫入存儲電容,因為選通三極管(就如讀取時一樣)與電容的充電必須要有一段時間,所以數據的真正寫入需要一定的周期。

六、突發讀寫

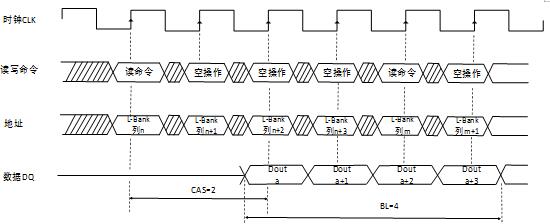

突發(Burst)是指在同一行中相鄰的存儲單元連續進行數據傳輸的方式,連續傳輸所涉及到存儲單元(列)的數量就是突發長度(Burst Lengths,簡稱BL)。前文講到的讀/寫操作,都是一次對一個存儲單元進行尋址,如果要想要連續的向SDRAM中讀數據或者寫數據,就需要對當前存儲單元的下一個單元進行尋址,也即是需要不停給SDRAM列激活信號以及讀/寫命令(行地址不變,所以不用再對行尋址)。雖然由于讀/寫延遲相同可以讓數據的傳輸在I/O端是連續的,但它占用了大量的內存控制資源,在數據進行連續傳輸時無法輸入新的命令,效率很低。為此,人們開發了突發傳輸技術,只要指定起始列地址與突發長度,SDRAM就會不再需要控制器連續地提供列地址,依次地自動對后面相應數量的存儲單元進行讀/寫操作。這樣,在突發模式讀寫中,除了第一個數據的傳輸需要若干個周期(主要是之前的延遲,一般的是tRCD+CL),其后每個數據只需一個周期的即可獲得。至于突發長度BL的數值,也是不能隨便設或在數據進行傳輸前臨時決定,而是在上文講到的SDRAM初始化過程中模式寄存器配置階段就要對突發長度進行設置。目前可用的選項是1、2、4、8、全頁(FullPage),常見的突發長度設定是BL=4、BL=8或者全頁突發模式。

圖5 突發讀時序圖

七、預充電

在進行完讀或寫操作后,接下來如果要對同一個L-Bank的另一行進行尋址,就要將原來有效的行關閉,重新發送行/列地址,這是由于SDRAM的尋址具有獨占性造成的。L-Bank關閉現有工作行,準備打開新行的操作就是預充電(Precharge)。實際上,預充電就是一種對工作行中所有存儲體進行數據重寫,并對行地址進行復位的操作。

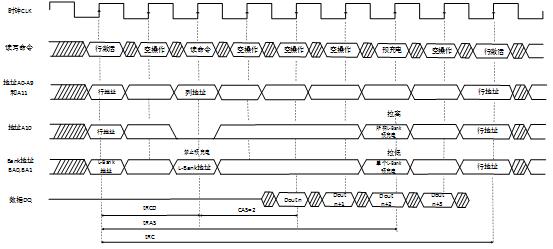

地址線A10控制著是否進行在讀或寫操作之后當前L-Bank自動進行預充電。在單獨的預充電命令中,A10控制著是對指定的L-Bank還是所有的L-Bank(當有多個L-Bank處于有效/活動狀態時)進行預充電,前者需要提供L-Bank的地址,后者只需將A10信號置于高電平。在發出預充電命令之后,要經過一段時間才能允許發送RAS行有效命令打開新的工作行,這個間隔被稱為tRP(Precharge command Period,預充電有效周期),單位是時鐘周期數,具體值視時鐘頻率而定。在實際的設計中,我們通常設計讓芯片每次讀寫操作后,自動進行預充電。這樣設計時就不需要再單獨考慮預充電的影響,只需要等待幾個時間周期即可。

圖6 讀數據預充電時序

上圖是突發長度設置為4、列選通潛伏期設置為2時,設置單獨預充電命令下的時序圖。可以看出,當行激活后,需要兩個時鐘周期的等待時間(tRCD)接收讀命令,SDRAM在接收讀命令時A10拉低,即此時不允許預充電,在SDRAM接收到預充電命令的時候才會進入預充電狀態。當接收到讀命令后,經過兩個周期的列地址選通(CAS)潛伏期從DQ數據線連續讀出4個數據。在預充電命令下,地址線A10拉高,SDRAM中所有L-Bank進入預充電狀態,從接收到行激活命令到接收預充電命令之間的時間間隔就是列選通脈沖拉高的周期數,從接收一個行激活命令到接收下一個行激活命令之間的間隔叫做tRC。