明德楊FPGA入門篇——Verilog計數器

作者:盧靖東

本文為明德揚原創文章,轉載請注明出處!

一、Verilog介紹

Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。Verilog HDL和VHDL是世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design Automation公司(該公司于1989年被Cadence公司收購)開發。兩種HDL均為IEEE標準。

二、Verilog計數器實測

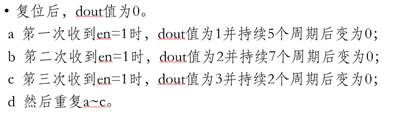

例題:

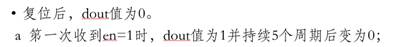

例題:

我們用 明德楊《至簡設計法》--八部計數法來分析此題

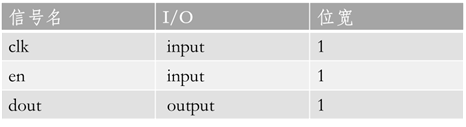

1.明確目標:找輸入輸出并繪畫I/O表

① 輸入輸出:

1.模塊時鐘,D觸發器中clk和rst_n為輸入,位寬默認為1。

2.題目給出輸出為dout,位寬和時鐘默認為1。

② I/O表:

2.畫波形圖

① 根據題目分析繪畫波形圖

先看第一個階段a部分:

完成第一階段后繼續后面的內容:

3.計數框架

① 計數結構:

以該題為例,題目要求多次收到en的信號,多個階段的信號處理,所以

我們可以優先考慮使用兩個計數器,命名為cnt_0和cnt_1,分別來記錄en=1

后dout處于哪個階段。

![]()

4.加一結束條件

u cnt_0加1條件:收到en的信號后,利用變量flag_add輔助來持續周期,所以cnt_0=flag_add為

加1條件。

u cnt_1加1條件:當cnt_0完成一個階段計數后,每收到en的信號,cnt_1就開始計數,完成一個階段cnt_1加1,所以 cnt_1=end_cnt_0 為加1條件。

5.定義特殊點

① 將需要的特殊點挑選出來,并用信號表示

① 將需要的特殊點挑選出來,并用信號表示

6.完整性檢查

保證每個信號的變化條件已經清晰明確,并且變化條件要用信號表示。

7.計數器代碼

? 計數器框架、加1條件和結束條件代碼

8.功能代碼

? 按照完整性檢查,寫出計數器之外的代碼。

最后仿真檢測一下代碼:

![]()

第一次接收到en信號

![]()

第二次接收到en信號

![]()

第三次接收到en的信號

以上就是Verilog計數器部分的內容分享,更多FPGA使用技巧加Q:2332395003交流學習!