二、基本概念

2.2硬件電路

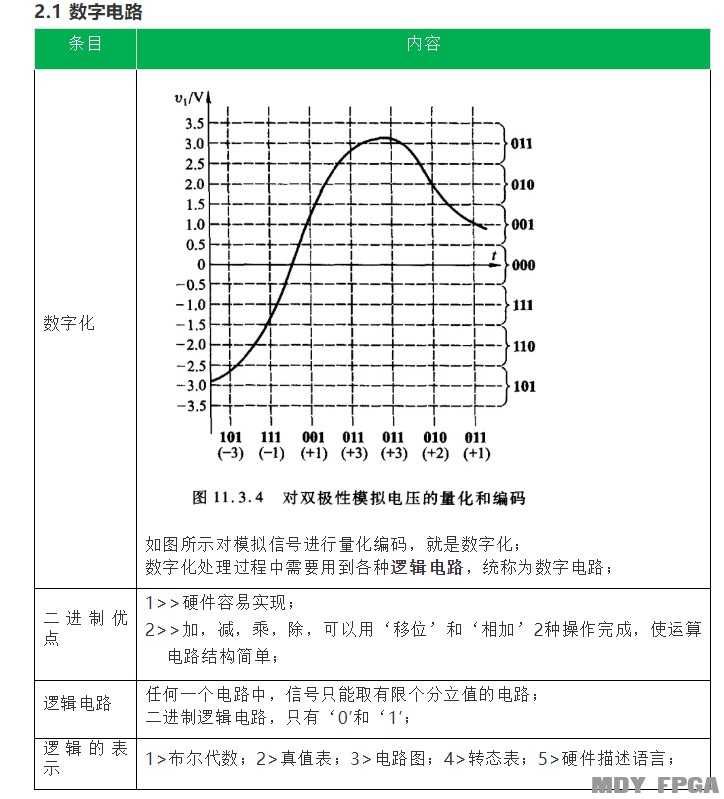

2.2 數制

2.2.1 進制轉換表

2.3 編碼

2.4 邏輯代數基礎

2.4.1 布爾代數

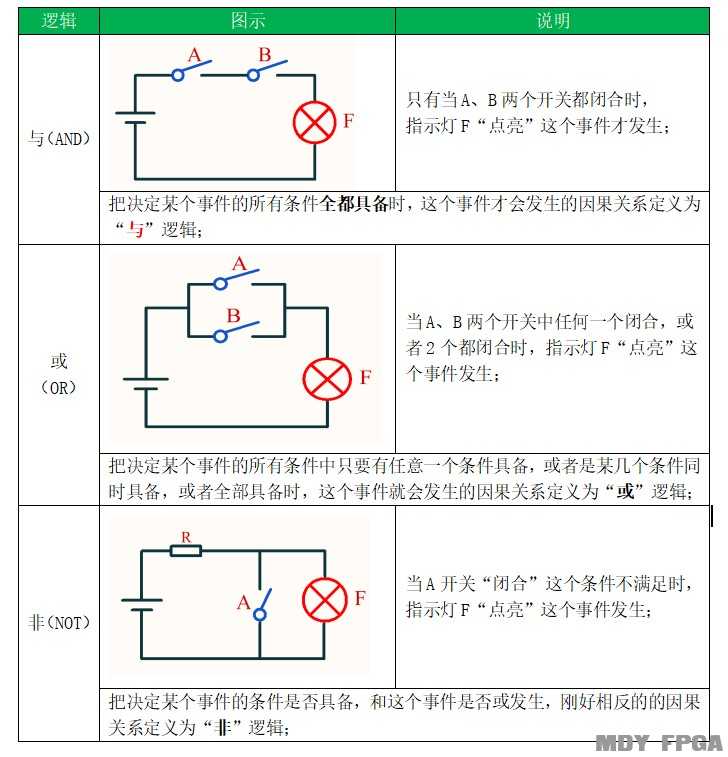

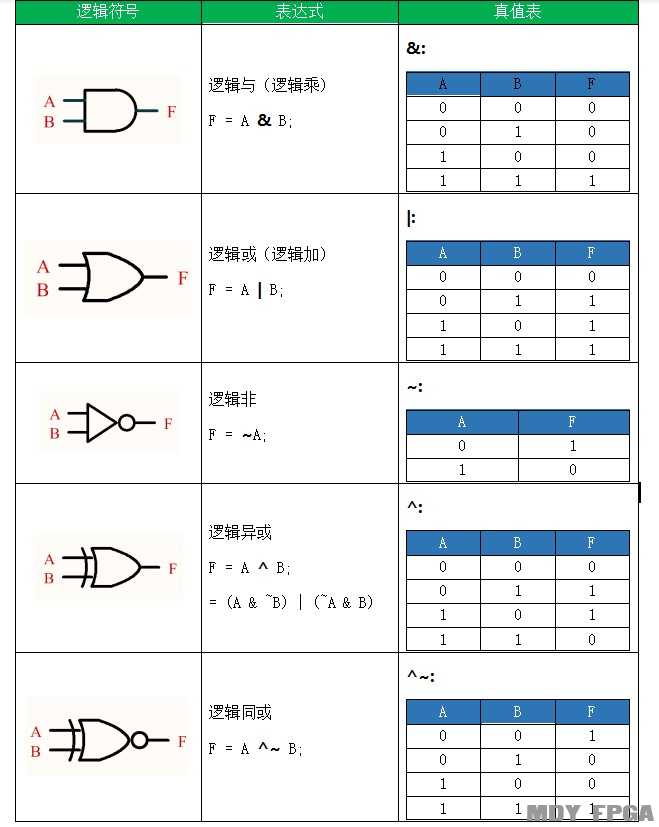

2.4.2 基本邏輯運算

2.4.3 基本邏輯表達

2.4.4 邏輯函數

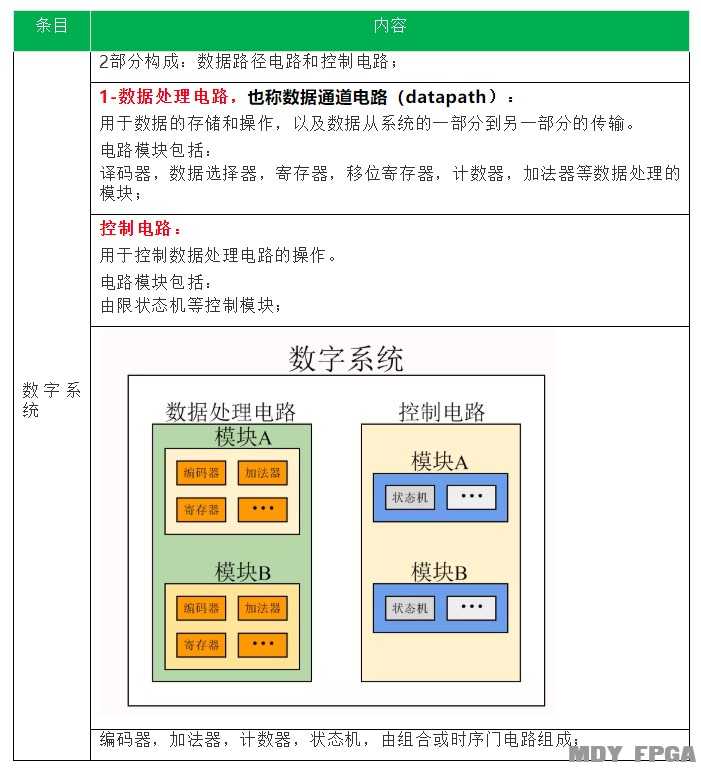

2.5 電路分類

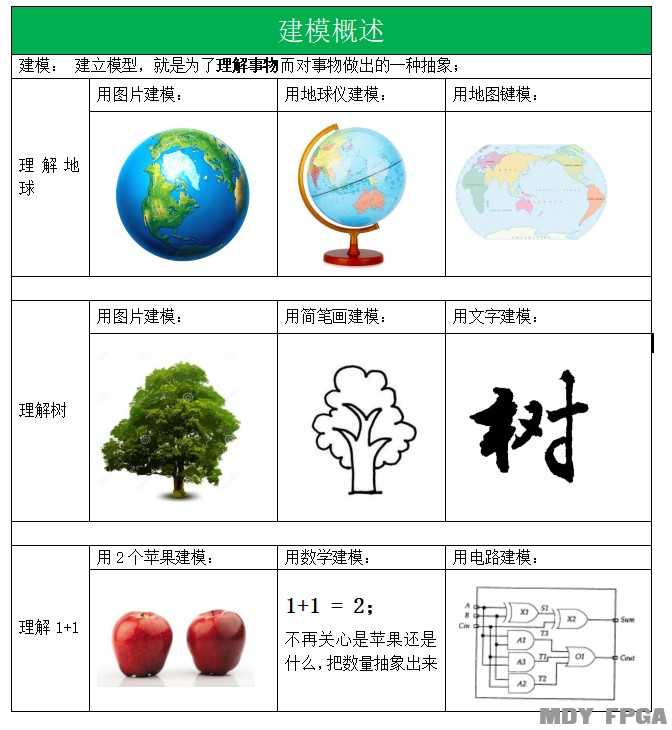

2.6 建模

2.6.1 建模概述

2.6.2 Verilog邏輯設計

三、 組合邏輯電路

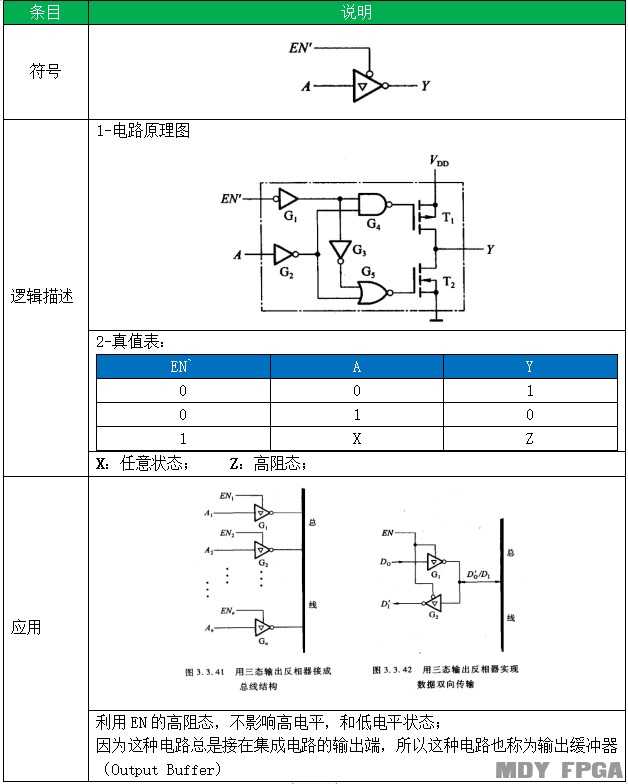

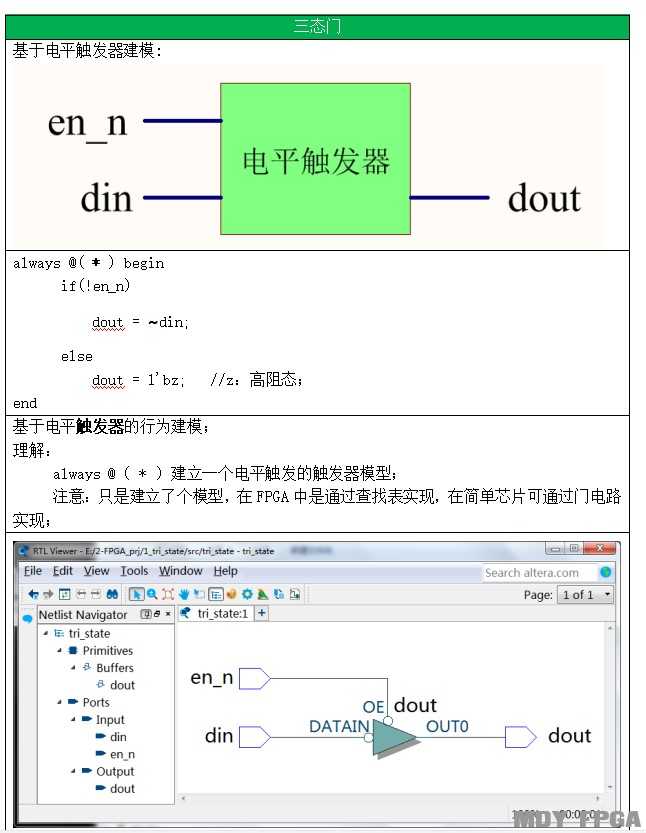

3.1 三態門3.1.1 工作原理

3.1.2 行為建模

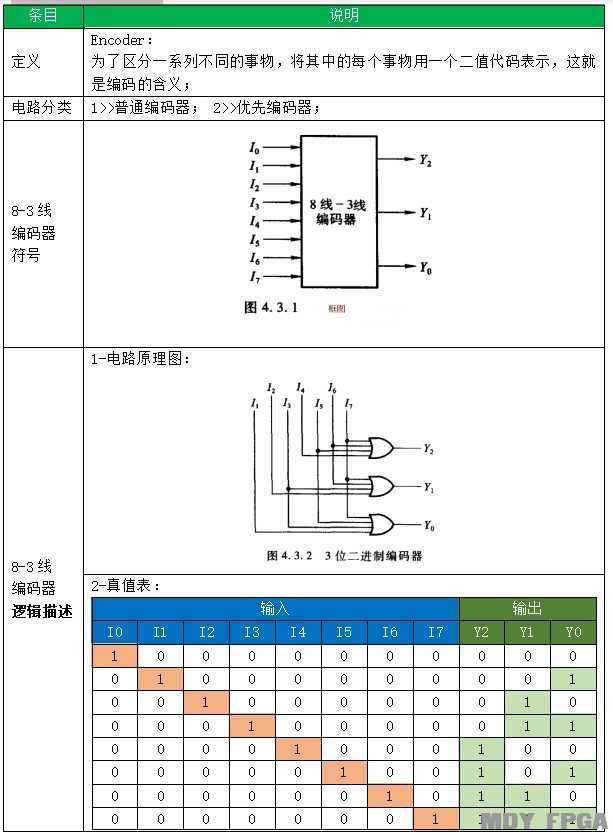

3.2 編碼器

3.2.1 工作原理

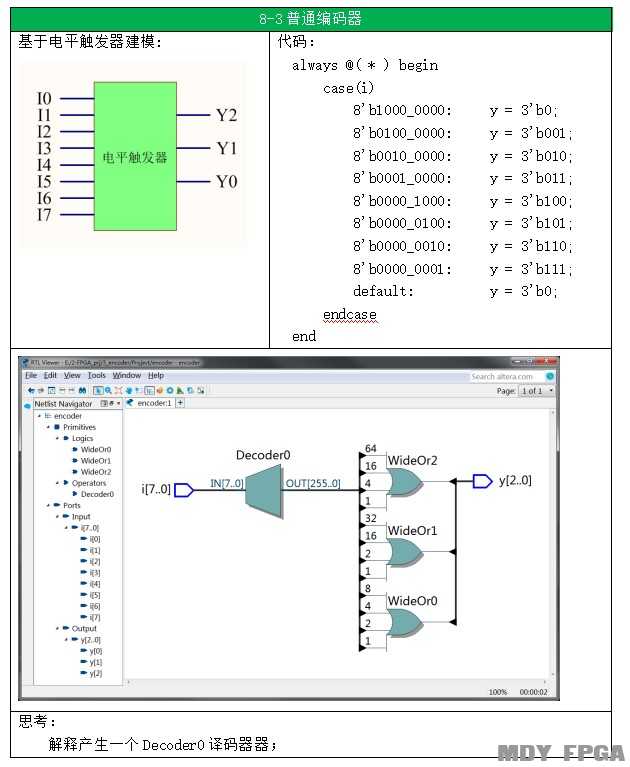

3.2.2 行為建模

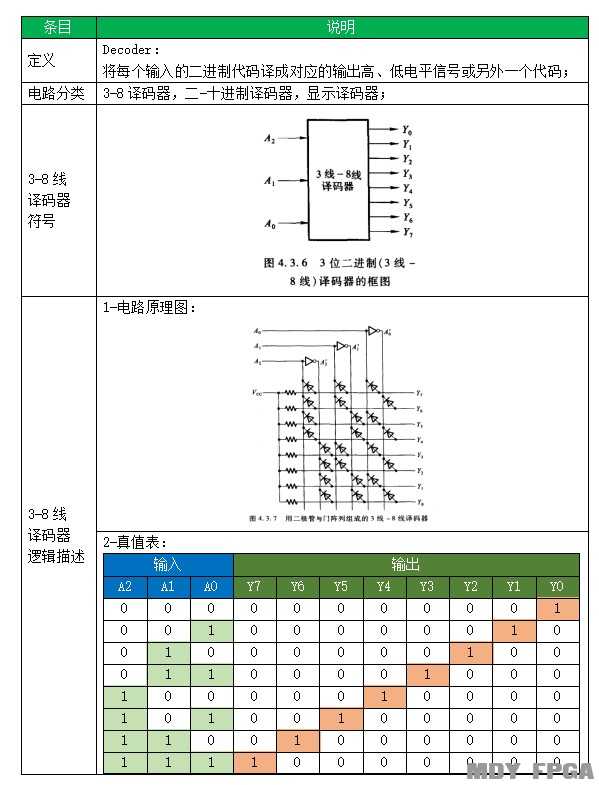

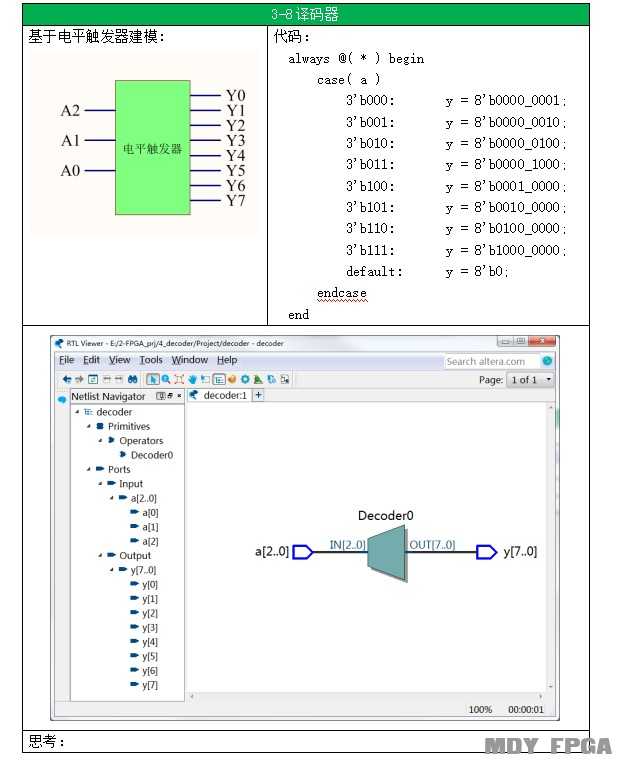

3.3 譯碼器

3.3.1 工作原理

3.2.2 行為建模

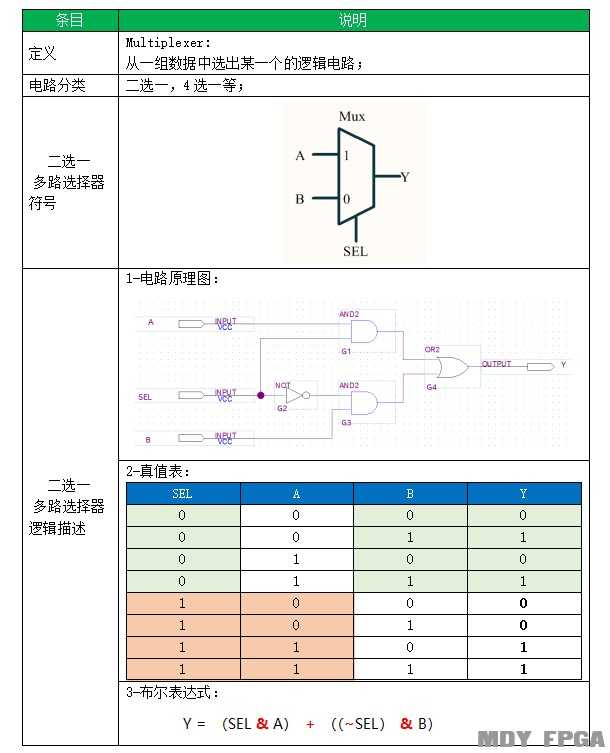

3.4 數據選擇器

3.4.1 工作原理

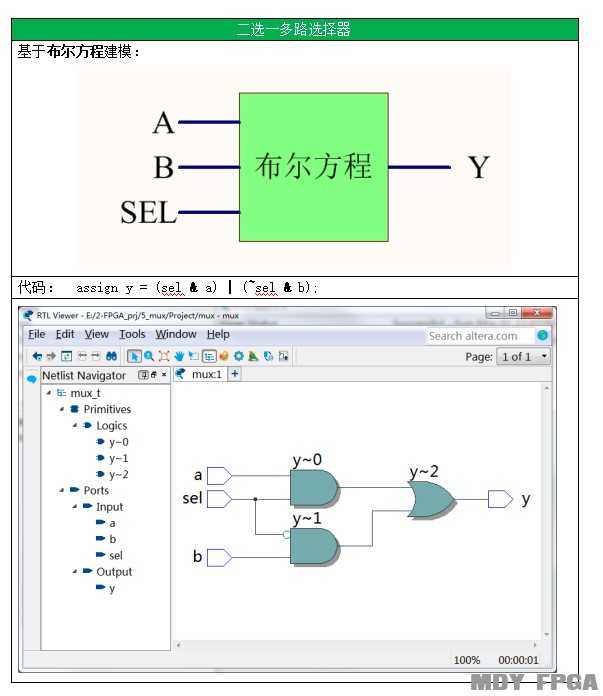

3.4.2 行為建模1

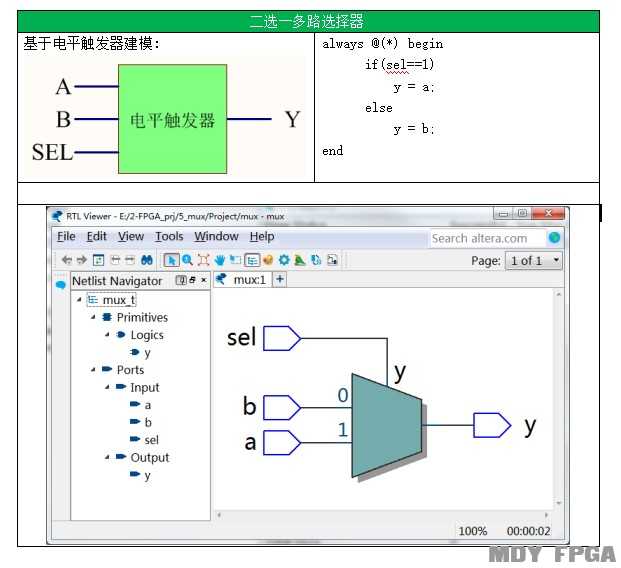

3.4.3 行為建模2

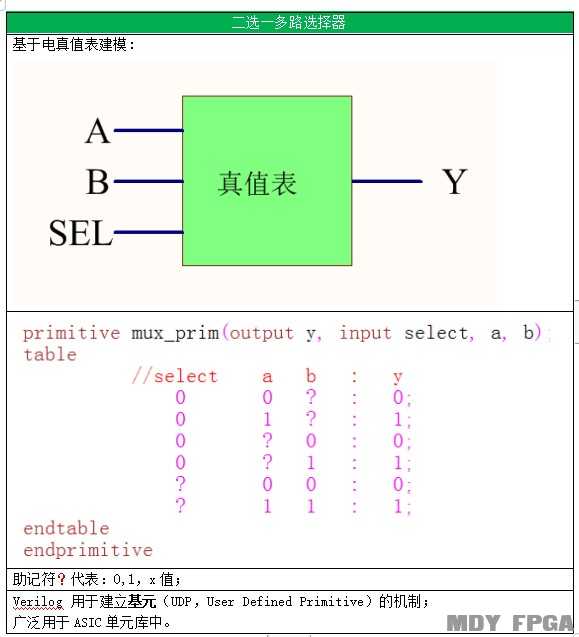

3.4.3 真值表建模

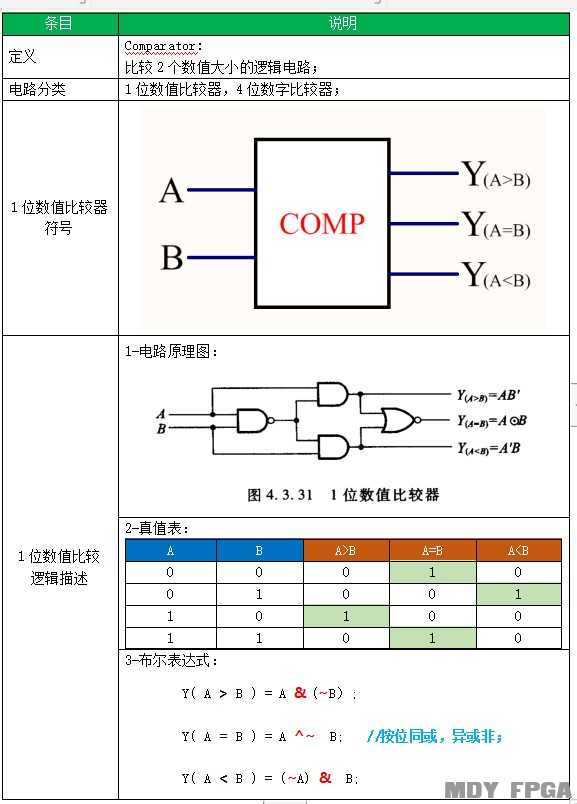

3.5.1 工作原理

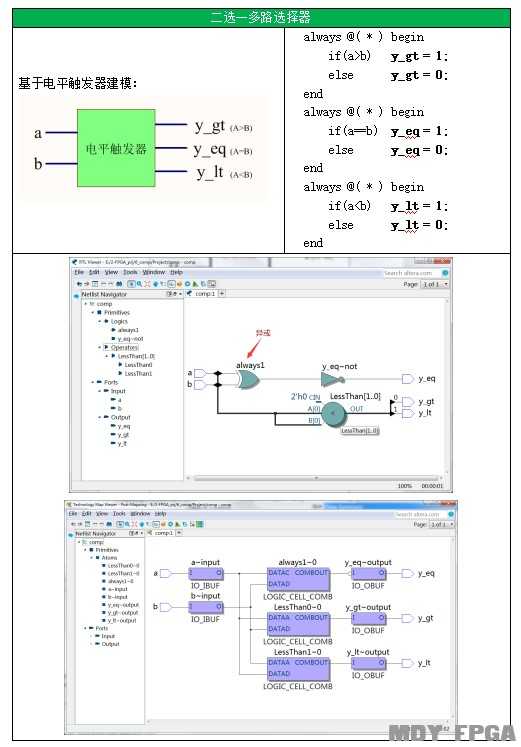

3.5.2 行為建模1

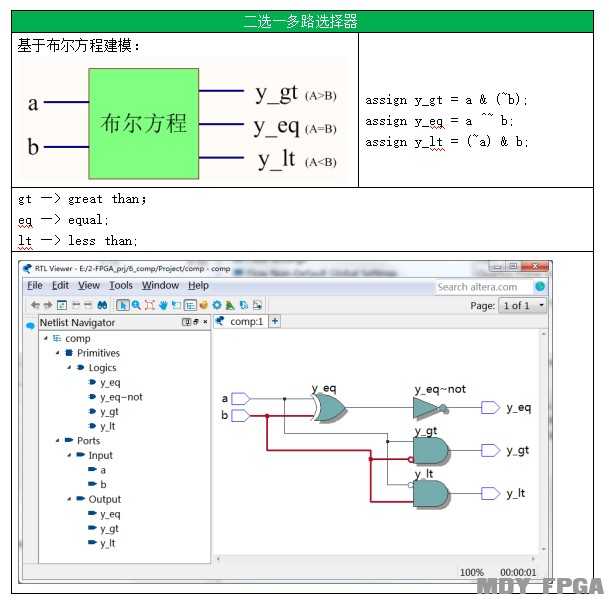

3.5.2 行為建模2

四、 時序邏輯電路

4.1 概述

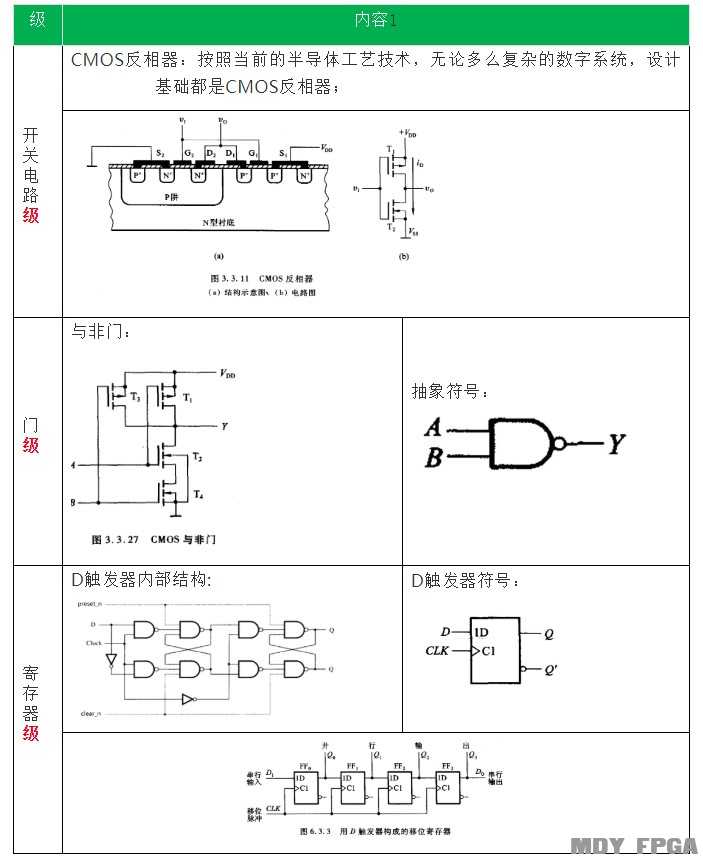

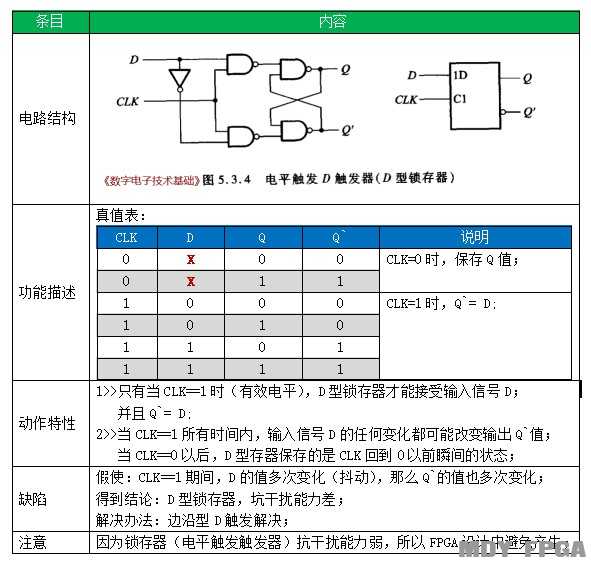

4.2 D型鎖存器

4.2 D型鎖存器

4.2.1 工作原理

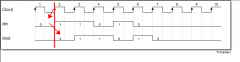

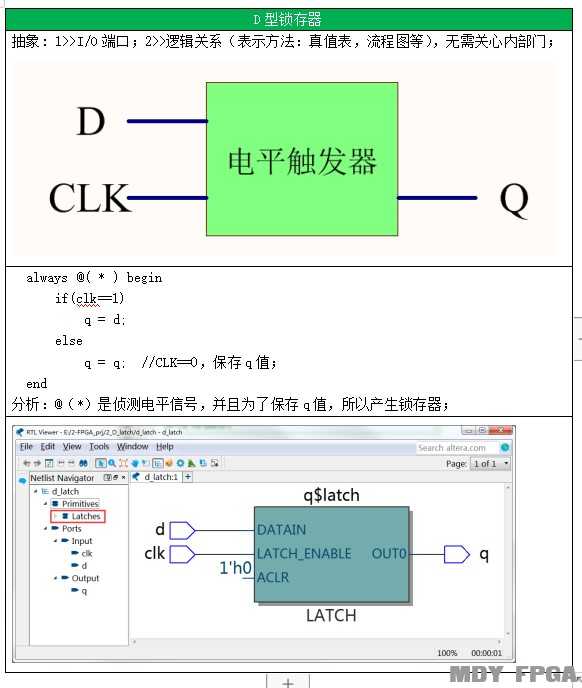

4.2.2 行為建模

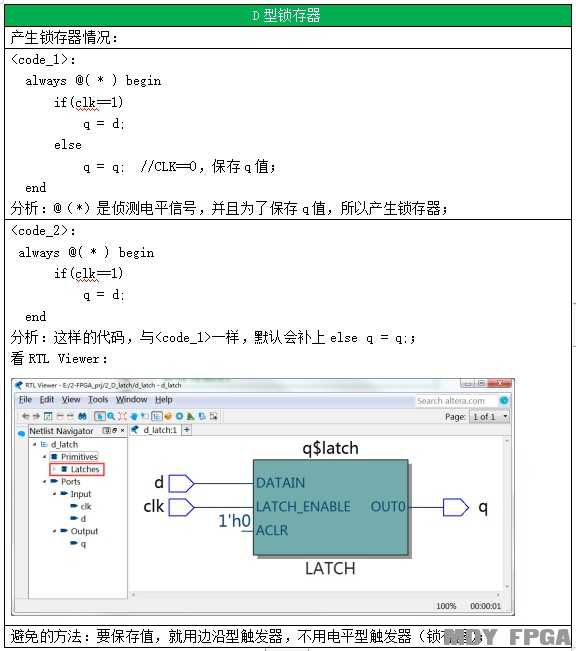

4.2.3 避免鎖存器

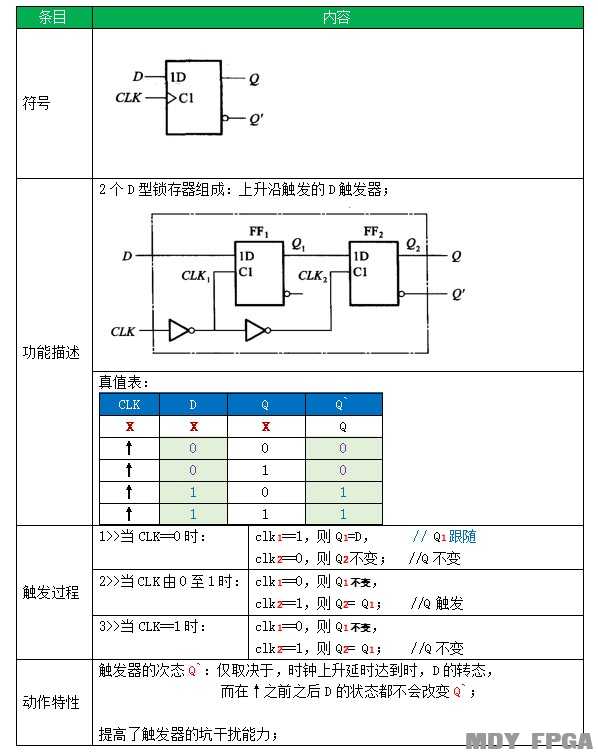

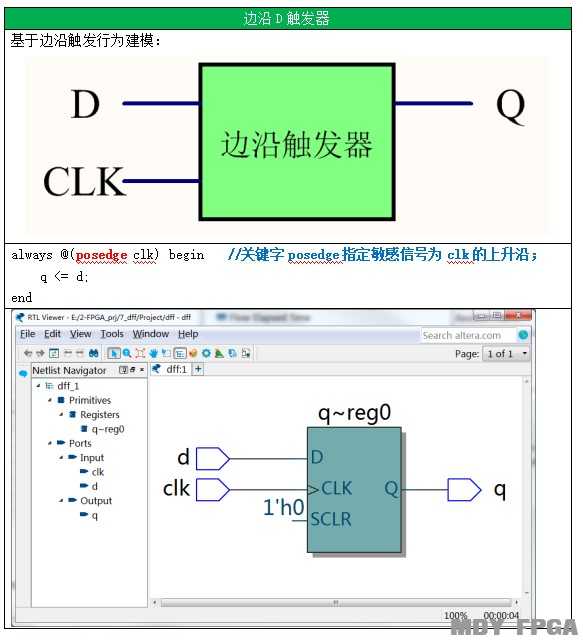

4.3.1 工作原理

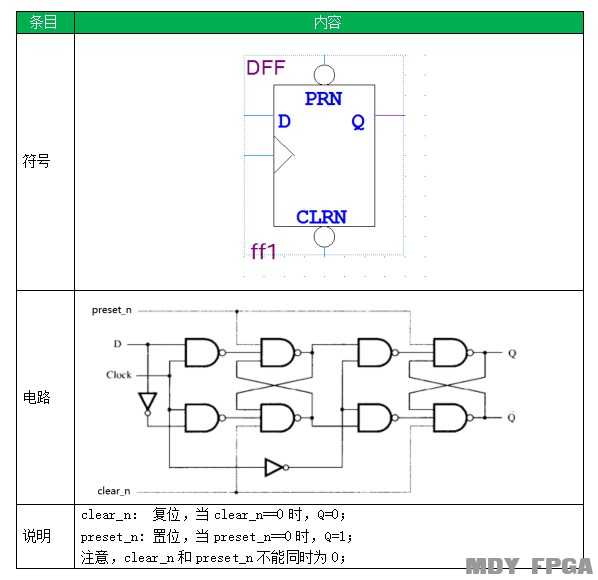

4.3.2 復位/置位D型觸器

4.3.3 行為建模

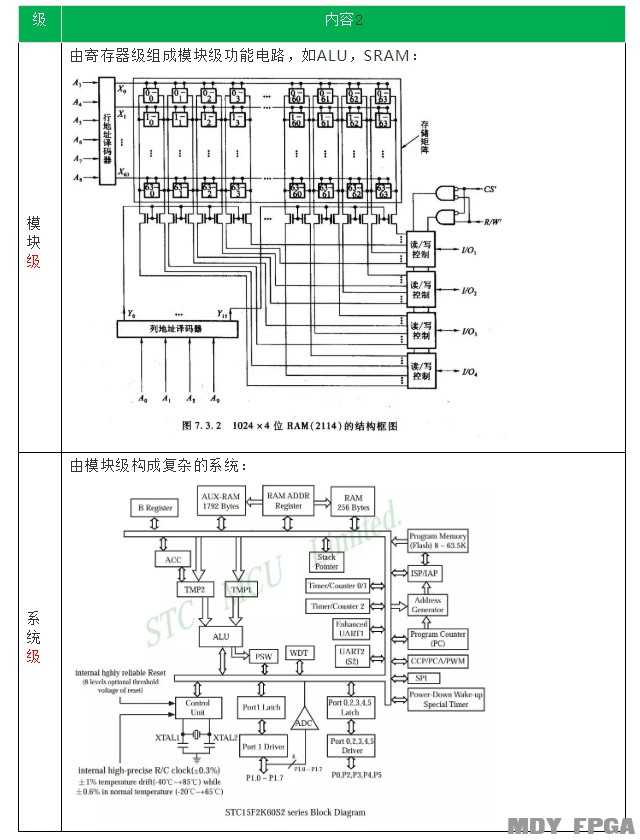

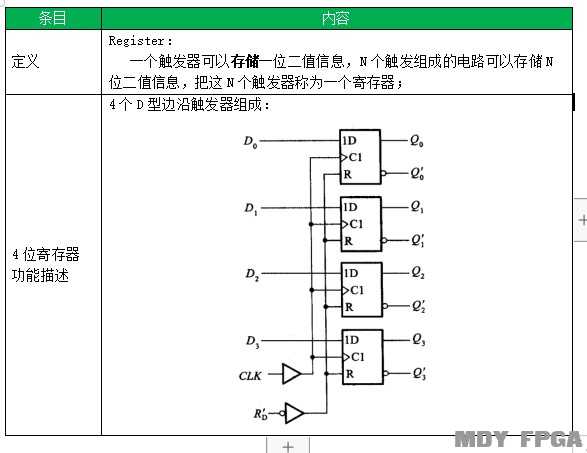

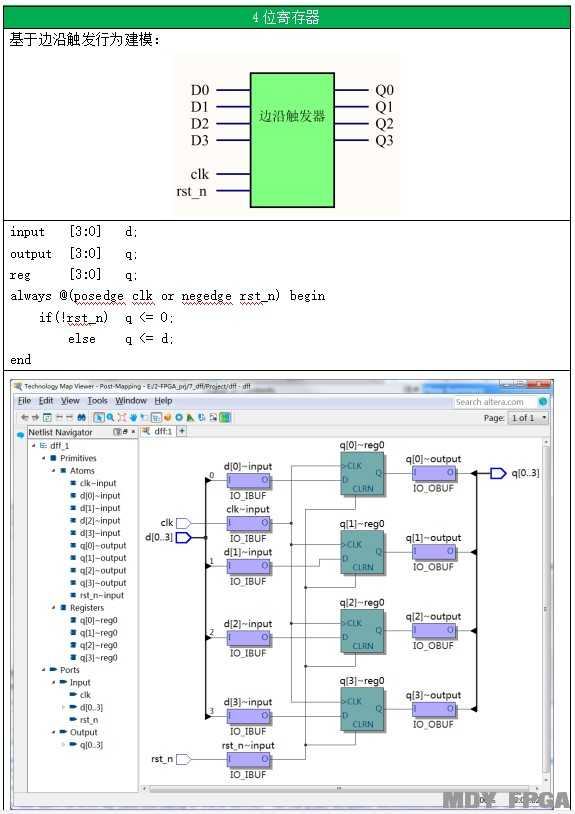

4.4 寄存器

4.4.1 工作原理

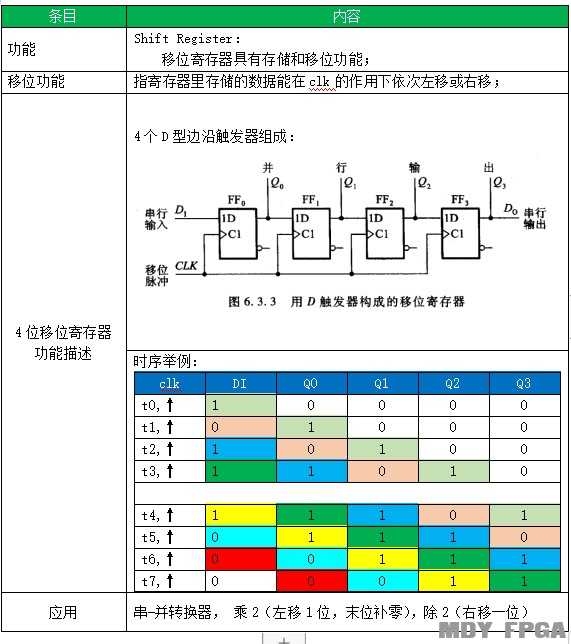

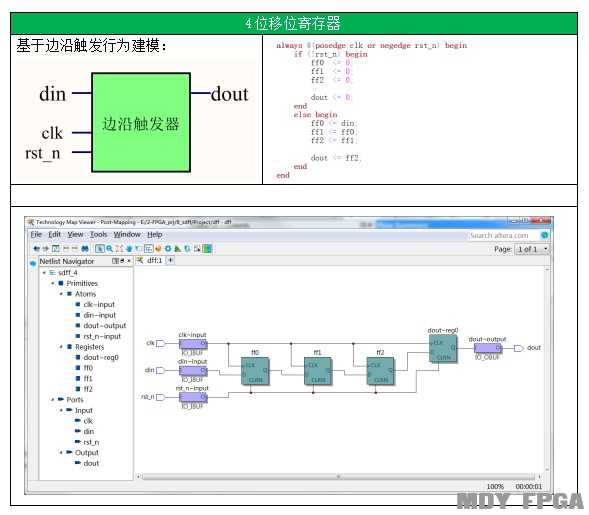

4.5 移位寄存器

4.5.1 工作原理

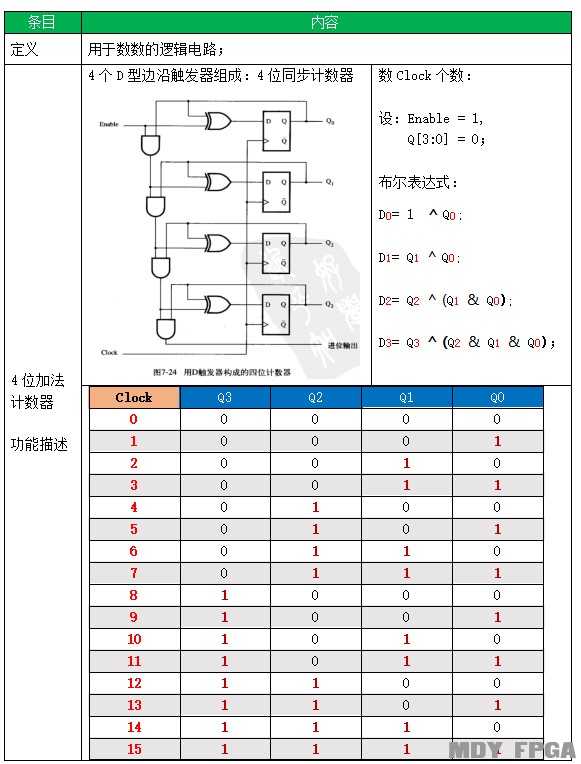

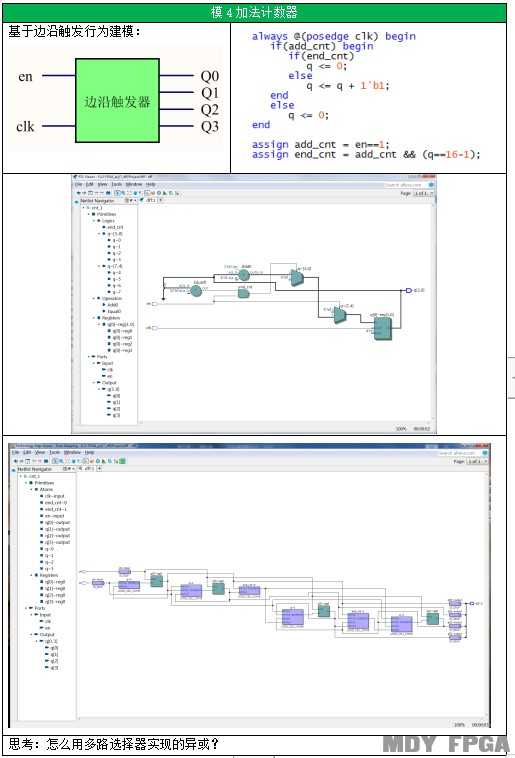

4.6 計數器

4.6.1 工作原理

4.6.2 行為建模

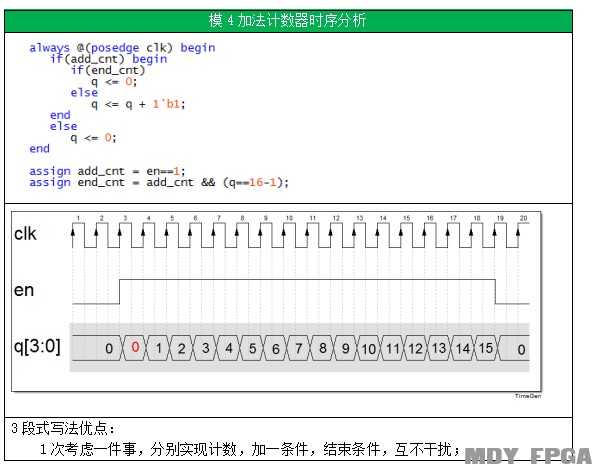

4.6.3 時序分析

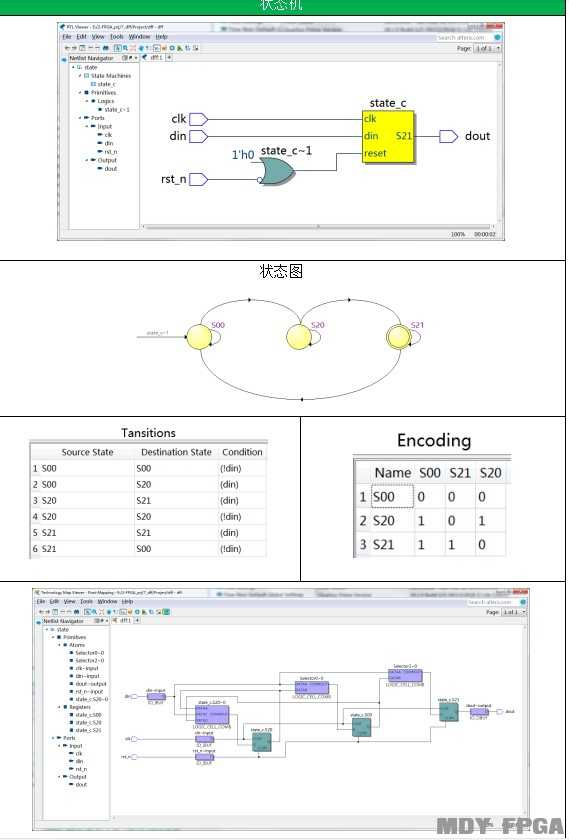

4.7 狀態機

4.6.1 概述

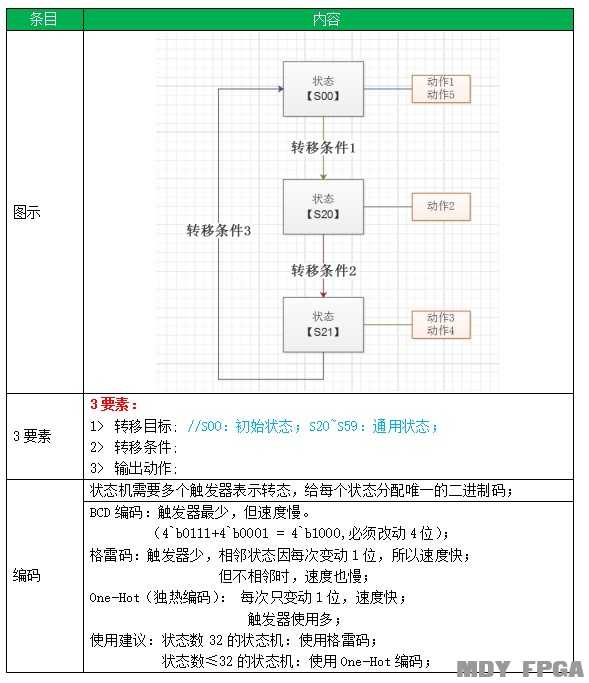

4.6.2 SFC

4.6.3 狀態機描述

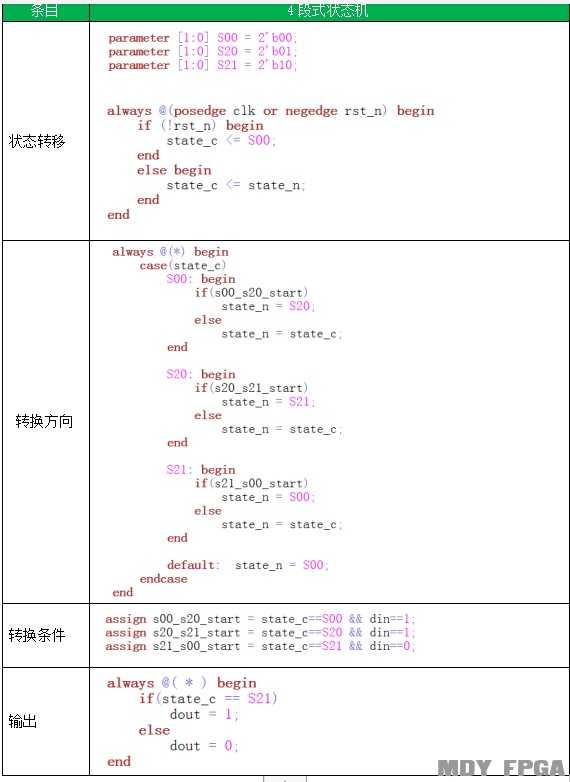

4.6.4 狀態機實現

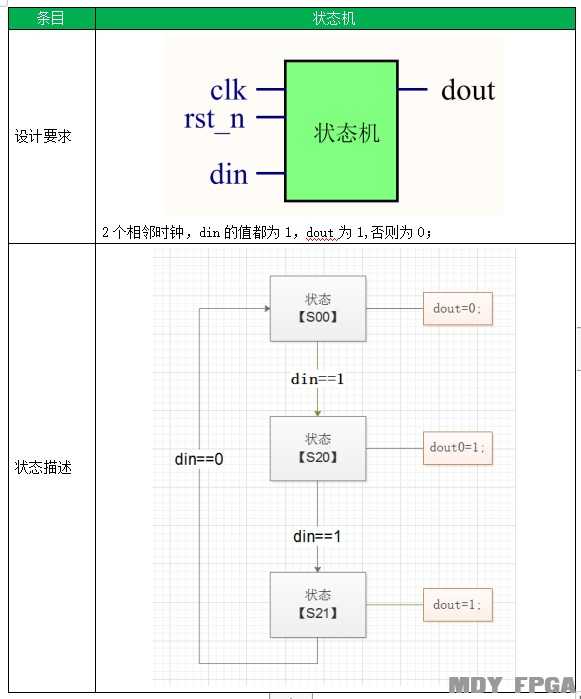

4.6.5 狀態機圖示

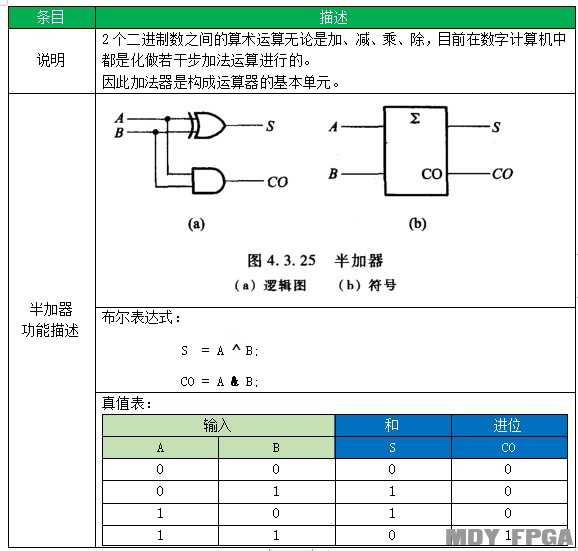

五、 算術運算電路

5.1 加法器

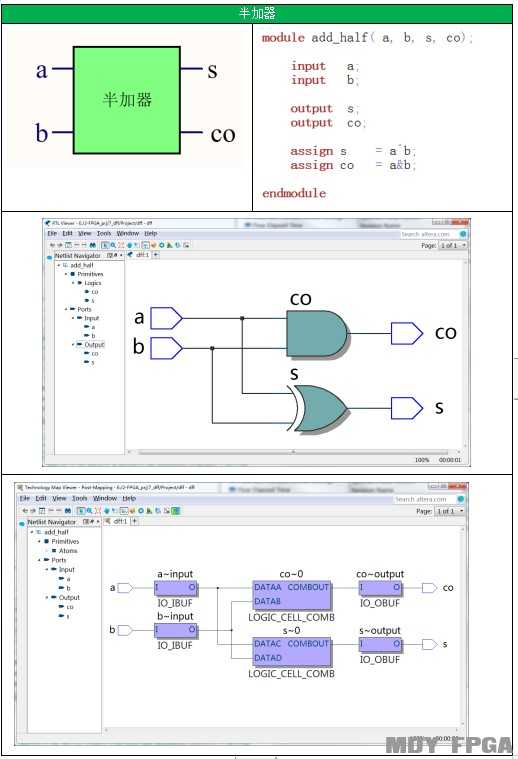

5.1.1 半加器工作原理

5.1.2 半加器行為建模

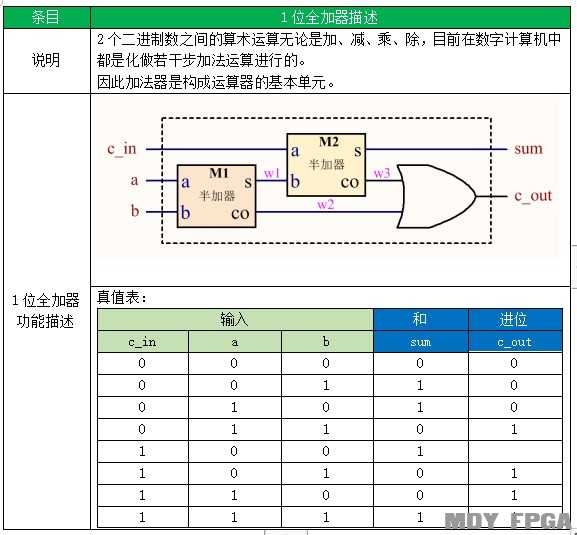

5.1.3 1位全加器工作原理

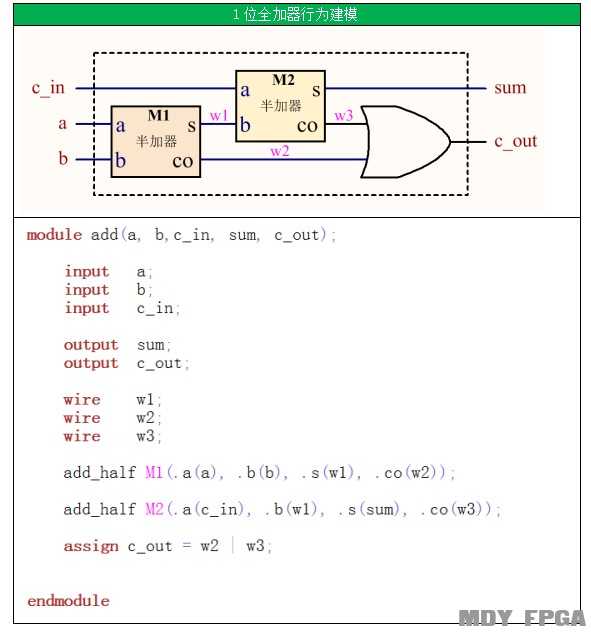

5.1.5 1位全加器行為建模

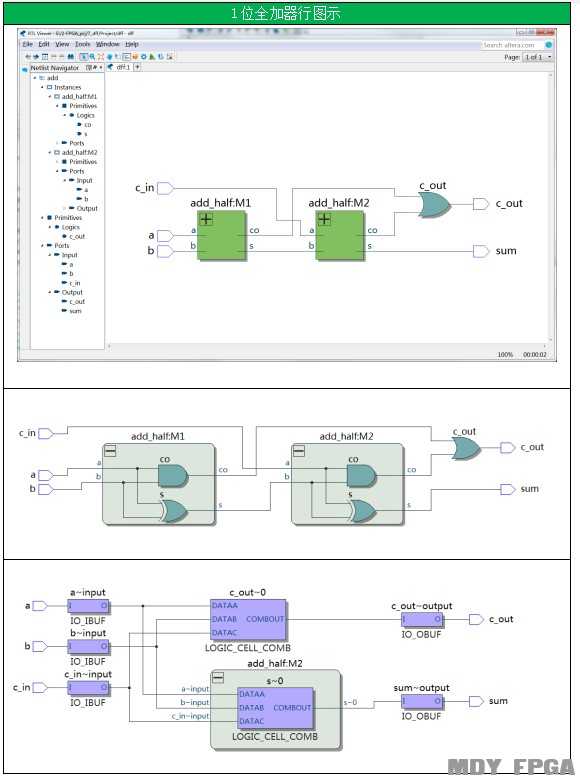

5.1.6 1位全加器行圖示

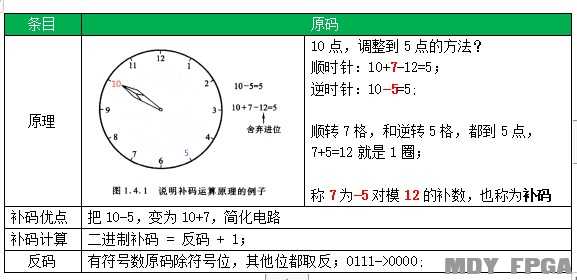

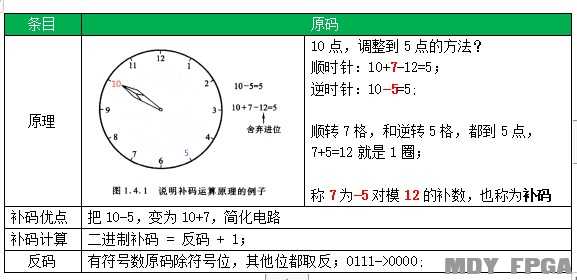

5.2 減法器5.2.1 原碼

5.2.1 補碼

5.2.1 補碼