PWM流水燈設(shè)計(jì)

--作者:小黑同學(xué)

【上板現(xiàn)象】PWM流水燈在MP801的上板現(xiàn)象(點(diǎn)擊跳轉(zhuǎn)明德?lián)P論壇觀看)

PWM流水燈在點(diǎn)撥開發(fā)板的上板現(xiàn)象(點(diǎn)擊跳轉(zhuǎn)明德?lián)P論壇觀看)

PWM流水燈在實(shí)驗(yàn)箱的上板現(xiàn)象(點(diǎn)擊跳轉(zhuǎn)明德?lián)P論壇觀看)

【設(shè)計(jì)教程】

1.1 總體設(shè)計(jì)

1.1.1 概述

脈沖寬度調(diào)制技術(shù)(Pulse WidthModelation,PWM)是利用微處理器/FPGA的數(shù)字輸出對(duì)模擬電路進(jìn)行控制的一種有效技術(shù),其廣泛應(yīng)用于測(cè)量、通信、功率控制與變換等眾多領(lǐng)域。PWM數(shù)字信號(hào)從處理器到被控系統(tǒng)都采用數(shù)字形式,無(wú)需進(jìn)行數(shù)模轉(zhuǎn)換。航模中的控制信號(hào)大多是PWM信號(hào),比如FUTABA、JR等舵機(jī)的控制都采用PWM方式,發(fā)射機(jī)給接收機(jī)輸送脈沖后接收機(jī)就會(huì)控制舵機(jī)進(jìn)行旋轉(zhuǎn)。舉個(gè)例子,假定基礎(chǔ)脈寬是100ms,當(dāng)發(fā)射機(jī)的脈寬增大(如增加到150ms)時(shí)接收機(jī)就控制舵機(jī)正向旋轉(zhuǎn);反之發(fā)射機(jī)的脈寬減小(如減小到50ms)時(shí),接收機(jī)就控制舵機(jī)逆向旋轉(zhuǎn)。

PWM是一種對(duì)模擬信號(hào)電平進(jìn)行數(shù)字編碼的方法。通過(guò)使用高分辨率計(jì)數(shù)器,對(duì)方波的占空比進(jìn)行調(diào)制,從而對(duì)一個(gè)具體模擬信號(hào)的電平進(jìn)行編碼。由于在給定的任何時(shí)刻,滿幅值的直流供電只存在有(ON)和無(wú)(OFF)兩種狀態(tài),因此PWM信號(hào)仍然是數(shù)字信號(hào)。電壓或電流源是以一種通(ON)或斷(OFF)的重復(fù)脈沖序列被加到模擬負(fù)載上去的。直流供電被加到負(fù)載上的時(shí)候?yàn)椤巴ā保?fù)載供電被斷開的時(shí)候?yàn)椤皵唷?。只要有足夠的帶寬,任何模擬值都可以使用PWM進(jìn)行編碼。

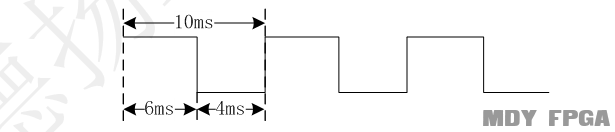

通俗來(lái)說(shuō),PWM是連續(xù)的、具有一定比例占空比的脈沖信號(hào),可以通過(guò)控制占空比來(lái)對(duì)其進(jìn)行改變。簡(jiǎn)單來(lái)說(shuō),可以認(rèn)為PWM就是一種方波,如圖所示是一個(gè)周期為10ms,高電平為6ms,低電平時(shí)間為4ms的PWM,其占空比(高電平時(shí)間占整個(gè)周期的比例)為60%

PWM波形圖

發(fā)光二極管簡(jiǎn)稱為LED,是一種常用的發(fā)光器件,通過(guò)電子與空穴復(fù)合釋放能量發(fā)光,它在照明領(lǐng)域應(yīng)用廣泛。發(fā)光二極管可高效的將電能轉(zhuǎn)化為光能,在現(xiàn)代社會(huì)具有廣泛的用途,如照明、平板顯示、醫(yī)療器件等??赏ㄟ^(guò)高低電平的變化來(lái)控制LED燈的明滅狀態(tài),當(dāng)輸出信號(hào)為低電平時(shí),LED燈亮,反之,當(dāng)輸出信號(hào)為高電平時(shí),LED燈滅。因此可通過(guò)改變PWM波形的占空比,來(lái)控制LED燈亮滅的時(shí)間,當(dāng)有多個(gè)LED燈的時(shí)候,通過(guò)不同的PWM波形來(lái)控制不同的LED燈,就可以產(chǎn)生各種各樣不同的效果。

1.1.2 設(shè)計(jì)目標(biāo)

本模塊產(chǎn)生8個(gè)不同的PWM脈沖,控制8個(gè)LED燈點(diǎn)亮不同的時(shí)間,從而達(dá)到流水燈的效果。每個(gè)脈沖周期為10s,占空比從10%~80%。上電后,led0點(diǎn)亮1s,熄滅9s;再點(diǎn)亮1s,熄滅9s,……,依次不斷循環(huán)。led1~led7與led0類似,分別點(diǎn)亮2s~8s,其他時(shí)候都是熄滅的。

1.1.3信號(hào)列表

1.1.4 設(shè)計(jì)思路

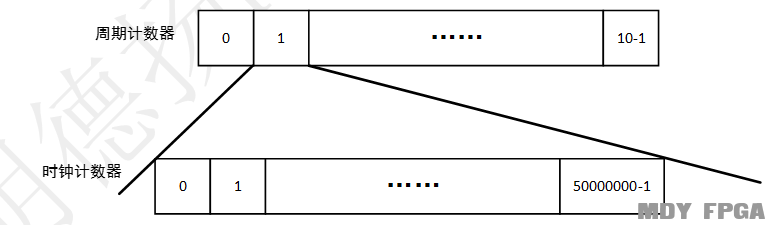

根據(jù)題目功能要求可知,產(chǎn)生的8個(gè)不同的PWM脈沖的周期都是10秒(s),由此我們可以提出兩個(gè)計(jì)數(shù)器的架構(gòu),如下圖所示。

該架構(gòu)由兩個(gè)計(jì)數(shù)器組成:時(shí)鐘計(jì)數(shù)器cnt_1s和周期計(jì)數(shù)器cnt_10s。

時(shí)鐘計(jì)數(shù)器cnt_1s:用于計(jì)算1秒的時(shí)鐘個(gè)數(shù),加一條件為1,表示一直計(jì)數(shù);結(jié)束條件為50000000,表示數(shù)到1秒就清零。

周期計(jì)數(shù)器cnt_10s:用于對(duì)1秒進(jìn)行計(jì)數(shù),加一條件為end_cnt_1s,表示數(shù)到1秒就加1;結(jié)束條件為10,表示數(shù)完10秒就清零。

至此,我們就將這個(gè)練習(xí)的計(jì)數(shù)器架構(gòu)設(shè)計(jì)出來(lái)了。

下面是計(jì)數(shù)器的代碼。

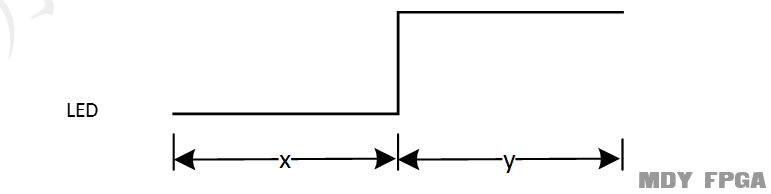

下面我們開始設(shè)計(jì)輸出信號(hào)led,在設(shè)計(jì)這些信號(hào)的時(shí)候,我們只需要關(guān)注他的變化點(diǎn),也就是0變1、1變0的點(diǎn)。

以led0的變化為例,上電后,led[0]點(diǎn)亮1s,熄滅9s,再點(diǎn)亮1s,熄滅9s。也就是數(shù)到1秒時(shí),即add_cnt_10s && cnt_10s==1-1時(shí),led0由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[0]由1變0。

Led[1]~led[7]也是同樣,即:

上電后,led[1]點(diǎn)亮2s,熄滅8s,再點(diǎn)亮2s,熄滅8s。也就是數(shù)到2秒時(shí),即add_cnt_10s &&cnt_10s==2-1時(shí),led[1]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[1]由1變0。

上電后,led[2]點(diǎn)亮3s,熄滅7s,再點(diǎn)亮3s,熄滅7s。也就是數(shù)到3秒時(shí),即add_cnt_10s &&cnt_10s==3-1時(shí),led[2]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[2]由1變0。

上電后,led[3]點(diǎn)亮4s,熄滅6s,再點(diǎn)亮4s,熄滅6s。也就是數(shù)到4秒時(shí),即add_cnt_10s &&cnt_10s==4-1時(shí),led[3]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[3]由1變0。

上電后,led[4]點(diǎn)亮5s,熄滅5s,再點(diǎn)亮5s,熄滅5s。也就是數(shù)到5秒時(shí),即add_cnt_10s &&cnt_10s==5-1時(shí),led[4]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[4]由1變0。

上電后,led[5]點(diǎn)亮6s,熄滅4s,再點(diǎn)亮6s,熄滅4s。也就是數(shù)到6秒時(shí),即add_cnt_10s &&cnt_10s==6-1時(shí),led[5]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[5]由1變0。

上電后,led[6]點(diǎn)亮7s,熄滅3s,再點(diǎn)亮7s,熄滅3s。也就是數(shù)到7秒時(shí),即add_cnt_10s &&cnt_10s==7-1時(shí),led[6]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[6]由1變0。

上電后,led[7]點(diǎn)亮8s,熄滅2s,再點(diǎn)亮8s,熄滅2s。也就是數(shù)到8秒時(shí),即add_cnt_10s &&cnt_10s==8-1時(shí),led[7]由0變1。當(dāng)數(shù)到10秒時(shí),即end_cnt_10s時(shí),led[7]由1變0。

由此便可以將所有的led信號(hào)設(shè)計(jì)出來(lái)。

下面是led的代碼。

1.1.5參考設(shè)計(jì)代碼

1.2 效果和總結(jié)

-

時(shí)間經(jīng)過(guò)1秒之后

-

時(shí)間經(jīng)過(guò)4秒的時(shí)候

-

時(shí)間經(jīng)過(guò)8秒的時(shí)候

看上面的現(xiàn)象,可以發(fā)現(xiàn),跟設(shè)計(jì)目標(biāo)要求的都是一樣的,成功完成設(shè)計(jì)目標(biāo)。

我們的至簡(jiǎn)設(shè)計(jì)法和計(jì)數(shù)器模板在以上的設(shè)計(jì)中發(fā)揮了至關(guān)重要的作用,使設(shè)計(jì)能夠快速準(zhǔn)確完成。本設(shè)計(jì)中的led信號(hào)的代碼為了方便理解,把8個(gè)led燈分開寫了,希望有興趣的同學(xué)可以將led的代碼進(jìn)行簡(jiǎn)化,合成一個(gè)always,想不到也沒(méi)關(guān)系,在講解視頻中也有講述如何實(shí)現(xiàn)。

感興趣的朋友也可以訪問(wèn)明德?lián)P論壇(http://www.fpgabbs.cn/)進(jìn)行FPGA相關(guān)工程設(shè)計(jì)學(xué)習(xí),也歡迎大家在評(píng)論與我進(jìn)行討論!

【設(shè)計(jì)教程下載】

【設(shè)計(jì)視頻教程】

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=1041&page=1&extra=#pid1805(點(diǎn)擊鏈接跳轉(zhuǎn)明德?lián)P論壇觀看)