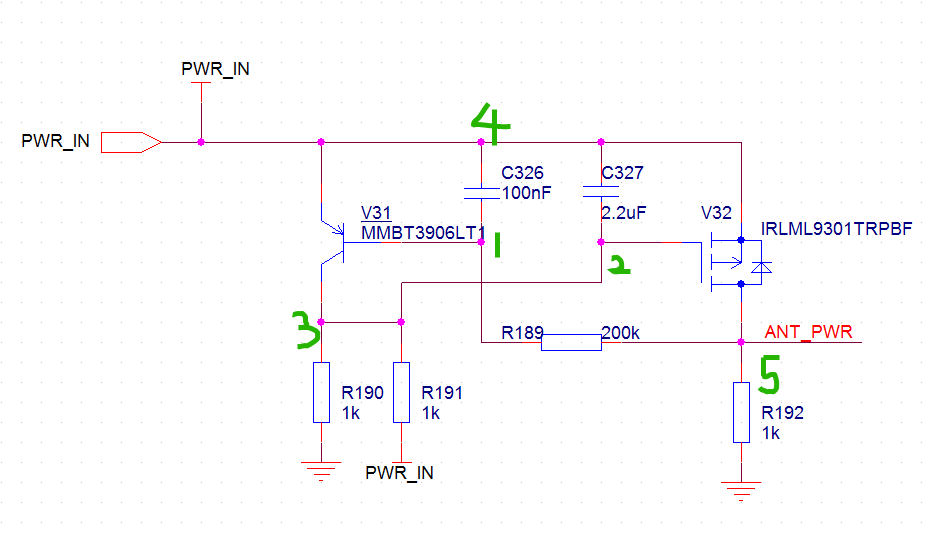

在使用有源天線時,天線熱插拔、甚至天線本身電路的故障可能會導致接收機饋電口發生短路、打火的情況。設計這個電路用于保護饋電口不會發生長時間短路,從而保護接收機和有源天線。電路僅采用了一個三極管和一個mos管以及若干阻容元件,成本低,可靠性高。除了用于保護饋電端口,也可以應用于許多其他的場景。...

基于Arria 10 FPGA的核心板電路研制

物聯網,智能汽車,云計算在我們生活中已經耳熟能詳,隨著FPGA的更新進步,在各類電子科技中不斷發力,讓我們的生活變得更加智能和便捷。下面給大家介紹一下來自Intel的FPGA Arria 10以及明德陽研發的一款Arria 10的核心板電路設計。...

原理圖和PCB設計中《0歐姆電阻的作用》

本文為明德揚原創文章,轉載請注明出處!1.引言深圳明德揚科技教育有限公司(簡稱MDY)研發了多款FPGA開發板(如MP5620、MP5705)、FPGA核心板(如MP5650、MP5652)以及FMC子板等模塊。在進行電路原理圖和PCB設計時,我們經常會使用到0歐姆電阻,實際上0歐姆電阻的并非真正的阻值為零歐姆,歐姆電阻實際是電阻值很小的...

FPGA視頻拼接項目LVDS視頻傳輸數據接口介紹

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術。由于其可使系統供電電壓低至 2V,因此它還能滿足未來應用的需要。此技術基于ANSI/TIA/EIA-644 LVDS 接口標準。LVDS 技術擁有 330mV 的低壓差分信號 (250mV MIN and 450mV MAX) 和快速過渡時間。 這可以讓產品達到自 100 Mbps 至超過 1 Gbps 的高數據速率。此外,這種低壓擺幅可以降低功耗消散,同時具備差分傳輸的優點。...

PCIE IP核介紹

PCIE是一種高速串行計算機擴展總線標準,屬于高速串行點對點雙通道高帶寬傳輸,所連接的設備分配獨享通道帶寬,不共享總線帶寬,支持主動電源的管理,錯誤報告,端對端的可靠性傳輸,熱插拔以及服務質量等功能。優點有數據傳輸速率高,發展潛力相當大。...

Xilinx官方的DP例程的建立步驟

明德揚(MDY)為某公司研制的被動立體轉主動立體視頻模塊,該模塊將3840×1080/60Hz視頻轉成1920×1080/120Hz視頻。視頻輸入接口為DP,輸出接口為DP和HDMI,基于Xilinx K7325t的高速收發器,特點是無需外圍接收/發送芯片,大大簡化了硬件設計。該視頻接口轉換模塊如圖1所示,其中k7核心板型號為MP5650,底板和核心板均為明德揚自研產品。...

AD9747混合模式的作用

背景 明德揚(MDY)在2022年承擔了多個高速ADC研發項目,今天給大家分享AD9747混合模式的作用。在ADDA系統中,AD前端采集到的帶通信號,經FPGA做數字信號處理后通過DAC進行數模轉換輸出。AD輸出采用欠采樣模式,FPGA數字信號處理的時鐘與AD時鐘相等,而DA的時鐘需要2倍以上的AD時鐘。...

高速ADC信噪比測試方法 與VisualAnalog的使用

明德揚(MDY)在2022年承擔了多個高速ADC研發項目,今天給大家分享高速ADC信噪比測試方法與VisualAnalog的使用!...