時序邏輯影響計數(shù)器精度

作者:陳刀刀

本文為明德?lián)P原創(chuàng)文章,轉載請注明出處!

本文將討論時序邏輯對明德?lián)P設計的計數(shù)器的計數(shù)精度的影響。由于FPGA是時序邏輯,只在時序上升沿時才統(tǒng)計一次,這意味著統(tǒng)計的精度只能是以“時鐘周期”為單位,即:存在小于一個時鐘周期信號無法采樣的情況。因為明德?lián)P計數(shù)器是在時鐘上升沿時判斷計數(shù)器是否加一,所以計數(shù)器的計數(shù)精度也是以“時鐘周期”為單位。

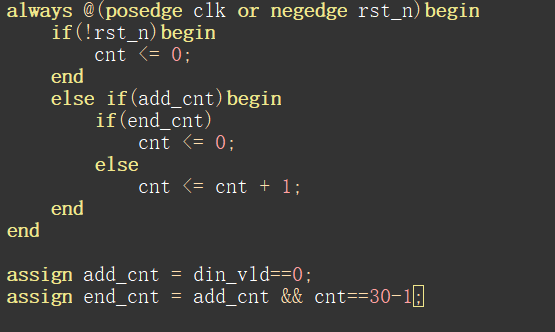

我們可以用一個例子來看一下計數(shù)器計數(shù)0時的一種誤差情況,假設有一個隨機的輸入din_vld,初值等于1,然后在一個任意時刻變?yōu)?。現(xiàn)在要計算din_vld變?yōu)?的前30個時鐘周期長度。計數(shù)器代碼如下圖:

計數(shù)器cnt在時鐘上升沿的時刻檢測到din_vld==0時cnt加一,所以cnt計算出來的是din_vld==0時cnt=0~29的30個時鐘周期。

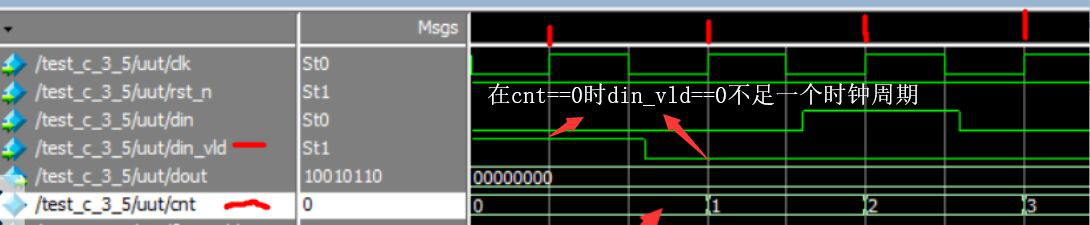

下圖為使用仿真軟件得出該代碼的波形,當din_vld不在時鐘上升沿的時刻變?yōu)?,則cnt==0時,din_vld==0的長度并不夠1個時鐘周期。因為時序邏輯影響計數(shù)器的精度是以“時鐘周期”為單位,所以并不影響計數(shù)器的計數(shù)。最終計算出來din_vld==0的前30個周期的長度,會產(chǎn)生長度為一個時鐘內的誤差。