時(shí)序約束系列之D觸發(fā)器原理和FPGA時(shí)序結(jié)構(gòu)

本文為明德?lián)P原創(chuàng)文章,轉(zhuǎn)載請(qǐng)注明出處!作者:姬姬姬

明德?lián)P有完整的時(shí)序約束課程與理論,接下來我們會(huì)一章一章以圖文結(jié)合的形式與大家分享時(shí)序約束的知識(shí)。要掌握FPGA時(shí)序約束,了解D觸發(fā)器以及FPGA運(yùn)行原理是必備的前提。今天第一章,我們就從D觸發(fā)器開始講起。

一、D觸發(fā)器的基本概念

1、D觸發(fā)器結(jié)構(gòu)

首先是D觸發(fā)器的結(jié)構(gòu),其硬件電路圖如下所示,可以看到D觸發(fā)器包含復(fù)位、時(shí)鐘、輸入和輸出;信號(hào)由D端輸入,clk給到上升沿的指示,Q端輸出信號(hào)。

D觸發(fā)器的功能很簡(jiǎn)單。

當(dāng)R等于0時(shí),q固定輸出0;

當(dāng)R等于1時(shí),遇到CLK的上升沿時(shí),將D的值賦給Q,D是什么Q就是什么;非CLK的上升沿,Q保持不變。

2、D觸發(fā)器代碼

D觸發(fā)器的代碼也很簡(jiǎn)單,如下圖所示,從代碼的描述來看,依舊是

當(dāng)rst_n等于0時(shí),q固定輸出0;

當(dāng)rst_n等于1時(shí),遇到clk的上升沿時(shí),將d的值賦給q,d是什么q就是什么;非clk的上升沿,q保持不變。

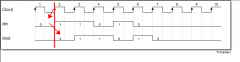

3、D觸發(fā)器波形

D觸發(fā)器工作波形如下所示,時(shí)鐘處于上升沿的時(shí),如果輸入信號(hào)D為1,輸出信號(hào)Q也為1;如果輸入信號(hào)D為0,那么輸出信號(hào)Q也為0。

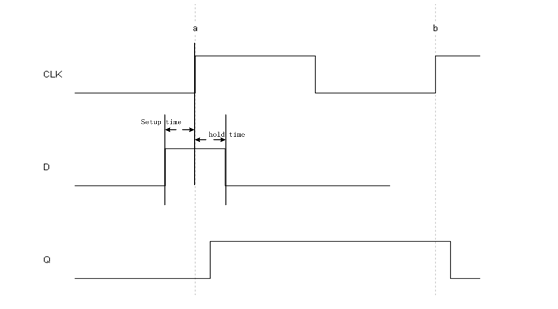

4、建立時(shí)間和保持時(shí)間

前面波形圖可以看到,D觸發(fā)器在上升沿處進(jìn)行信號(hào)采集,為了保證采集到的數(shù)據(jù)準(zhǔn)確性,信號(hào)D在上升沿前后會(huì)保持狀態(tài)一段時(shí)間。在上升沿前的這段時(shí)間為setup_time,叫做建立時(shí)間;上升沿后的這段時(shí)間為hold_time部分,叫做保持時(shí)間。

關(guān)于建立時(shí)間和保持時(shí)間有幾個(gè)關(guān)鍵點(diǎn)需要注意。

首先D觸發(fā)器的數(shù)據(jù)輸入端必須在建立時(shí)間前到達(dá),并且要保持到持續(xù)時(shí)間以后,這樣才可以保證FPGA可以采集到正確的數(shù)據(jù)。

其次建立時(shí)間和保持時(shí)間是D觸發(fā)器的固有屬性,是不可改變的。注意,這里說的不可改變,是指不能從代碼層次去改變。例如我們買了一個(gè)FPGA開發(fā)板,其FPGA芯片的D觸發(fā)器建立時(shí)間和保持時(shí)間就是固定的,沒辦法從VERILOG去修改,除非換一個(gè)芯片。

二、電路的延時(shí)

1、電路延時(shí)原理

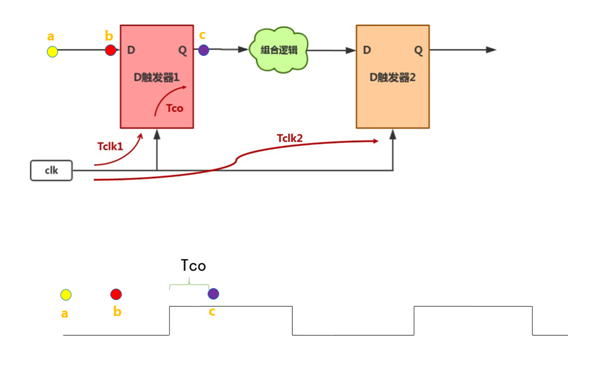

我們知道從物理層面看電平通過每個(gè)階段都是需要一段時(shí)間的,這就是電路的延時(shí),我們通過FPGA中最經(jīng)典的結(jié)構(gòu)來學(xué)習(xí)一下電路的延時(shí)。使用了兩個(gè)D觸發(fā)器,中間由組合邏輯進(jìn)行相連,即通過一個(gè)組合邏輯電路將兩個(gè)D觸發(fā)器相連。電路圖如下圖所示:

從圖中可以看出,一個(gè)有效信號(hào)經(jīng)過D觸發(fā)器1之后,接著經(jīng)過一段組合邏輯(可以是加法器、選擇器、乘法器這些電路,也可以僅僅是連線)然后到達(dá)另一個(gè)D觸發(fā)器2,D觸發(fā)器2對(duì)信號(hào)進(jìn)行判斷后繼續(xù)進(jìn)行輸出。下面逐個(gè)分析這個(gè)基本結(jié)構(gòu)里面包含的時(shí)間參數(shù)。

首先Tclk1是時(shí)鐘到D觸發(fā)器1的時(shí)間。Tclk2為時(shí)鐘到達(dá)D觸發(fā)器2的時(shí)間,在真實(shí)的物理情況下,因?yàn)橛芯€路的延時(shí),兩個(gè)時(shí)鐘采到的上升沿其實(shí)是不同的,有一點(diǎn)微小的差別;但是FPGA里面,我們經(jīng)常把這個(gè)時(shí)間忽略掉,因?yàn)槲覀?span>FPGA時(shí)鐘時(shí)專門優(yōu)化過的,它們之間的差別會(huì)比較小,因此在這里我們先忽略不計(jì)。Tclk1和Tclk2是時(shí)鐘延時(shí)。

還有一段時(shí)間為D觸發(fā)器的傳輸延時(shí),即上升沿之后,采集到的數(shù)據(jù)從進(jìn)入到出來這段時(shí)間延時(shí)。如下圖所示,輸出信號(hào)Q在上升沿后一段時(shí)間由0變1,這段為D觸發(fā)器的傳輸延時(shí)。

接著D觸發(fā)器1之后信號(hào)需要通過組合邏輯賦到D觸發(fā)器2之前的位置,這段時(shí)間是組合邏輯的延時(shí),即信號(hào)通過組合邏輯這段時(shí)間的延時(shí)為組合邏輯延時(shí)Tdata。

最后還有前面講到的建立時(shí)間和保持時(shí)間,信號(hào)在D觸發(fā)器2會(huì)有建立時(shí)間和保持時(shí)間,這就是D觸發(fā)器本身的延時(shí)。

2、時(shí)序表示電路的延時(shí)

這里我們可以用時(shí)序來表示這組結(jié)構(gòu)中的信號(hào)變化。如下所示,比如我們有兩個(gè)時(shí)鐘上升沿,在最開始,所有位置的信號(hào)都為0。

假設(shè)一個(gè)由0變1的信號(hào)需要通過前面的組合邏輯,首先D觸發(fā)器1前面一段由0變1,即圖中點(diǎn)a到點(diǎn)b變?yōu)?span>1,這段時(shí)間在時(shí)序中如下圖中點(diǎn)a與點(diǎn)b的位置。

1)D觸發(fā)器傳輸延時(shí)

接著是D觸發(fā)器的傳輸延時(shí),在時(shí)鐘上升沿處,信號(hào)1從D觸發(fā)器1后輸出,即下圖中信號(hào)從c點(diǎn)輸出,這段時(shí)間的延時(shí)在時(shí)序中為時(shí)鐘上升沿處到信號(hào)輸出的延時(shí),即下面時(shí)序圖中Tco部分。

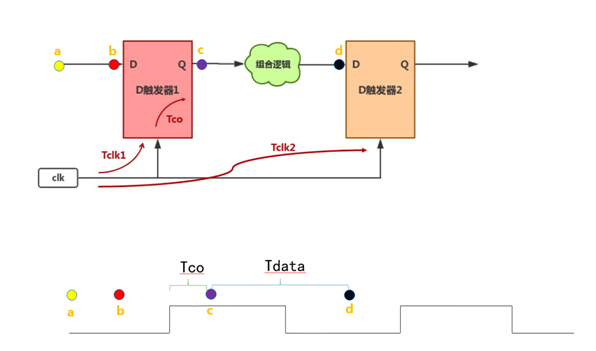

2)組合邏輯延時(shí)間

之后信號(hào)會(huì)通過組合邏輯,這段時(shí)間為組合邏輯的延時(shí)Tdata。如下圖所示,此信號(hào)由點(diǎn)c通過組合邏輯接著傳輸?shù)近c(diǎn)d,在時(shí)序圖中為Tdata部分。

3)建立時(shí)間

當(dāng)然不要忘記我們前面講的D觸發(fā)器傳輸信號(hào)會(huì)有一段的建立時(shí)間,因此在時(shí)序中信號(hào)1會(huì)提前到達(dá)d點(diǎn),即信號(hào)到達(dá)d點(diǎn)時(shí),到達(dá)下一個(gè)時(shí)鐘上升沿還有一段時(shí)間,如下面時(shí)序圖中Tus部分所示。

當(dāng)然像上圖中這樣信號(hào)到達(dá)d點(diǎn)的時(shí)間與建立時(shí)間相等的情況是比較理想的狀態(tài),現(xiàn)實(shí)工程中大多數(shù)情況下信號(hào)1都會(huì)提前到達(dá)d點(diǎn),等待建立時(shí)間的到來,即時(shí)間預(yù)量。實(shí)際的時(shí)序圖如下所示,可以看到信號(hào)達(dá)到d點(diǎn)的時(shí)間與D觸發(fā)器建立時(shí)間并不重合,中間會(huì)有一段時(shí)間預(yù)量,這才是實(shí)際工程中可以見到的情況。

以上就是由0變1的信號(hào)通過兩個(gè)D觸發(fā)器和一段組合邏輯的流程。在理想狀態(tài)下整個(gè)過程的延時(shí)與時(shí)間周期是相等的,但是實(shí)際情況下會(huì)有一定的變化,這時(shí)需要我們具體問題具體分析。

三、D觸發(fā)器在FPGA中的使用

1、FPGA的電路結(jié)構(gòu)

了解了兩個(gè)D觸發(fā)器的組合使用,下面學(xué)習(xí)FPGA的基本電路結(jié)構(gòu)。

FPGA的基本電路結(jié)構(gòu)如上圖所示。我們可以把電路分成兩個(gè)部分:D觸發(fā)器和組合邏輯。每?jī)蓚€(gè)D觸發(fā)器之間,都會(huì)有或多或少的組合邏輯。組合邏輯可以是乘法器、加法器、RAM,甚至就是一條簡(jiǎn)單的連線。前一個(gè)D觸發(fā)器的輸出端,經(jīng)過組合邏輯運(yùn)算后,給了下一個(gè)D觸發(fā)器的輸入端,等待時(shí)鐘上升沿的時(shí)候,再傳遞給D觸發(fā)器的輸出端。

上圖中,所有的D觸發(fā)器都統(tǒng)一受時(shí)鐘CLK的控制,都是在CLK的上升沿把輸入的值傳遞給輸出端。

FPGA中有4個(gè)組合邏輯A、B、C、D ,邏輯與邏輯之間,共使用了5個(gè)D觸發(fā)器傳輸數(shù)據(jù)。其中組合邏輯A持續(xù)20納秒,組合邏輯B持續(xù)40納秒,組合邏輯C持續(xù)50納秒,組合邏輯D持續(xù)35納秒。時(shí)鐘周期為100納秒,即上升沿100納秒產(chǎn)生一次;每個(gè)觸發(fā)器的建立時(shí)間為5納秒,保持時(shí)間為25納秒。

2、現(xiàn)實(shí)案例

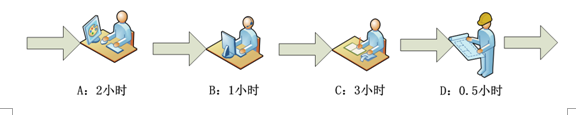

為了便于理解,我們用一個(gè)生活中的例子類比一下D觸發(fā)器與組合邏輯的關(guān)系。如下圖所示,現(xiàn)在有一個(gè)生產(chǎn)線生產(chǎn)一款產(chǎn)品,一共需要4個(gè)步驟,分別由員工ABCD來完成,其中A做完一個(gè)工序需要2小時(shí),B需要1小時(shí),C需要3小時(shí),D是0.5小時(shí)。工廠統(tǒng)一規(guī)定每隔5個(gè)小時(shí)交接一次;為了避免交接混亂,要求交接點(diǎn)前5分鐘交接,交接點(diǎn)后10分鐘才能繼續(xù)工作。

此生產(chǎn)線就像是前面我們講到的FPGA電路結(jié)構(gòu),四個(gè)員工就相當(dāng)于FPGA中四個(gè)組合邏輯,大家在同一個(gè)環(huán)境下工作,被同一個(gè)時(shí)鐘所支配,相互間又有著傳輸關(guān)系。

要求每5個(gè)小時(shí)交接一次相當(dāng)于100納秒產(chǎn)生一次時(shí)鐘上升沿;每一位員工交接給下一位員工的這個(gè)過程就相當(dāng)于D觸發(fā)器將輸入的值賦給輸出。

所有員工在交接點(diǎn)前5分鐘都停下手中工作,進(jìn)入準(zhǔn)備交接狀態(tài),5分鐘相當(dāng)于D觸發(fā)器的建立時(shí)間5納秒;交接點(diǎn)后10分鐘,大家依舊保持交接狀態(tài),10分鐘相當(dāng)于D觸發(fā)器的保持時(shí)間25納秒。

公司的規(guī)定必須提前5分鐘,等待10分鐘進(jìn)行交接,就和D觸發(fā)器的硬件特性相同,交接時(shí)間是不能因?yàn)閭€(gè)人改變的;不論工作什么時(shí)候完成,在交接點(diǎn)前5分鐘一定要準(zhǔn)備交接,交接點(diǎn)后保持交接狀態(tài)10分鐘才可以繼續(xù)工作,這樣才可以保證整個(gè)生產(chǎn)線可以流暢進(jìn)行。

我們用了一個(gè)簡(jiǎn)單的案例比較清晰的理解了D觸發(fā)器,通俗來說就是需要傳輸?shù)臄?shù)據(jù)等待在D觸發(fā)器前,D觸發(fā)器每個(gè)時(shí)鐘都會(huì)在門口進(jìn)行檢測(cè),檢測(cè)到了有效數(shù)據(jù)后,在此時(shí)鐘上升沿進(jìn)行數(shù)據(jù)輸出。

以上就是明德?lián)P時(shí)序約束課程中D觸發(fā)器部分的相關(guān)知識(shí),想要獲取時(shí)序約束相關(guān)資料的同學(xué)可以加Q 1744527324(明德?lián)P小冉)了解!