在Verilog中,wire永遠是wire,就是相當于一條連線,用來連接電路,不能存儲數據,無驅動能力,是組合邏輯;并且只能在assign左側賦值,不能在always @ 中賦值。

reg可以綜合成register,latch,甚至是wire(當其只是中間變量的時候),能存儲數據,有驅動能力,可以用于組合邏輯或者時序邏輯;在always @模塊表達式左側被賦值。

掌握了基本原理,并不代表我們可以快速的判斷信號類型。我們在實際設計中,并不需要考慮這么多,對于信號類型的定義,明德揚有一個小技巧,按照這個技巧使用,就不會出錯。即“用always實現的是reg型,其它都是wire型”。

我們舉幾個例子來使用一下此技巧。

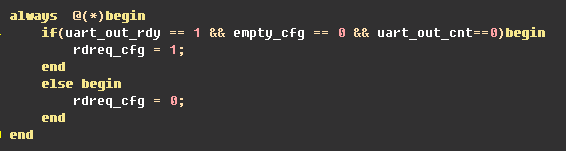

案例一:

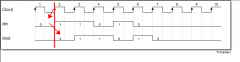

下面代碼可以看出是由always模塊引導的,因此屬于reg類型:

案例二:

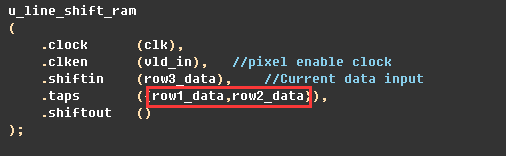

下面代碼不是由always模塊引導的,因此屬于wire類型:

案例三:

下面代碼是由always模塊引導的,因此屬于reg類型:

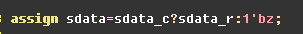

案例四:

下面代碼是由assign模塊引導的,不是由always模塊引導的,因此屬于wire類型:

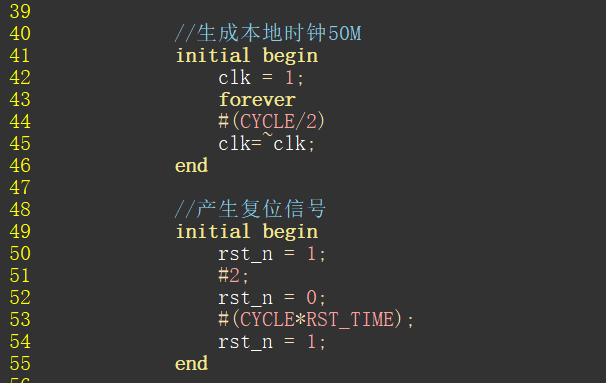

案例五:

在測試文件中,凡是initial模塊引導的信號都是reg類型,因此下面代碼屬于reg類型:

掌握了信號類型的原理,就非常好判斷信號的類型了。大家試著多看一些案例設計進行驗證,就會發現明德揚的小技巧非常好用。因此希望大家可以牢記,定義信號類型時,用always實現的是reg型,其它都是wire型。如果可以完全掌握并多加應用,今后的工程師道路會節省不少的腦細胞。更多FPGA技巧敬請關注明德揚,有疑問的同學也可以留言給我們互相討論!

reg、wire怎么確定?明德揚總結了以下的3句話,大家記好啦:

1、功能文件:由本模塊產生,并且用always產生的信號,就定義成reg

2、測試文件:由初始化產生(一般是對測模塊的輸入)的信號,就定義成reg

3、除了以上兩種情況,就定義成wire型