本文為明德揚原創文章,轉載請注明出處!

本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用:

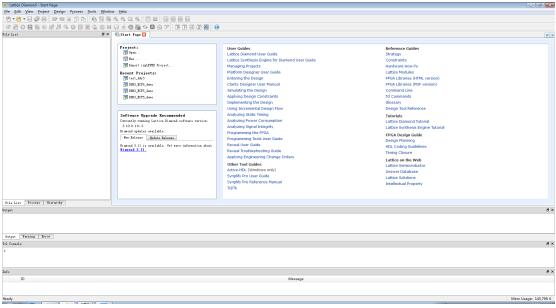

一、建立Lattice工程

1、首先,新建一個工程“lattice_ddr3”:

其中器件選擇的是ECP5U系列LFE5U-45F-CABGA381芯片,Lattice的工程后綴是.ldf文件。進入工程界面后,添加模塊文件:右鍵點擊Input Files --Add--New File--Verilog Files即可添加。

2、添加了工程文件后,需要設置一個頂層,右鍵點擊impl1,選擇Set Top-Level unit,在彈出的窗口中設置頂層文件的名稱,綜合軟件選擇系統自帶的Lattice LSE。

二、頂層文件設計

頂層文件中,需要包含輸入輸出信號,其中系統的輸入是時鐘clk和復位信號rst_n,輸出是FPGA向DDR3的輸出信號,信號的流程圖如下所示:

其中,IP核控制模塊Mem_burst中是雙端口的輸入輸出,輸入信號有頂層中產生的輸入和IP核返回的輸入信號;輸出有IP核輸出到Mem_burst的信號和控制模塊輸出到頂層的信號。

三、模塊信號功能介紹:

DDR3 IP核的調用主要有兩部分模塊,分別是控制模塊和IP核接口模塊,其對應的各信號列表如下:

1、控制模塊的信號功能列表如下所示:

|

信號名 |

位寬 |

I/O |

功能 |

|

clk |

1 |

I |

工作時鐘,由IP核輸出時鐘sclk提供 |

|

rst_n |

1 |

I |

復位信號,低電平有效 |

|

rd_burst_req |

1 |

I |

外部輸入讀請求信號 |

|

wr_burst_req |

1 |

I |

外部輸入寫請求信號 |

|

rd_burst_addr |

28 |

I |

外部輸入讀請求地址 |

|

wr_burst_addr |

28 |

I |

外部輸入寫請求地址 |

|

rd_burst_data_valid |

1 |

O |

控制模塊讀出到外部的有效數據 |

|

wr_burst_data_req |

1 |

O |

控制模快輸出到外部的寫請求確認信號,外部收到此信號,開始寫入數據 |

|

rd_burst_data |

64 |

O |

控制模塊輸出到外部的數據 |

|

wr_burst_data |

64 |

I |

外部輸入的寫數據 |

|

burst_finish |

1 |

O |

|

|

app_rst_n |

1 |

O |

控制器輸出的IP核復位信號 |

|

app_init_start |

1 |

O |

控制器輸出的IP核初始化開始信號 |

|

app_cmd |

4 |

O |

控制器輸出的IP核指令信號 |

|

app_cmd_valid |

1 |

O |

控制器輸出的IP核指令有效信號 |

|

app_addr |

28 |

O |

控制器輸出的IP核地址信號 |

|

app_cmd_burst_cnt |

1 |

O |

命令突發計數輸出,指示給定的讀或寫命令被控制器自動重復的次數。控制器還根據命令的突發長度順序生成每個重復命令的地址 |

|

app_ofly_burst_len |

1 |

O |

控制器輸出的當前命令及時突發長度 |

|

app_write_data |

64 |

O |

控制器輸出給IP核的外部寫入數據 |

|

app_data_mask |

8 |

O |

用于寫數據的數據掩碼。每個位屏蔽本地寫數據的對應字節 |

|

app_init_done |

1 |

I |

IP核輸入的初始化完成信號 |

|

app_cmd_rdy |

1 |

I |

IP核輸入的命令準備信號 |

|

app_datain_rdy |

1 |

I |

IP核輸入的數據寫入準備信號 |

|

app_read_data |

64 |

I |

IP核輸入的從DDR3中輸出的數據 |

|

app_read_data_valid |

1 |

I |

IP核輸入的讀出數據有效信號 |

|

app_wl_err |

1 |

I |

IP核輸入的寫錯誤指示信號 |

|

app_rt_err |

1 |

I |

IP核輸入的讀錯誤指示信號 |

2、DDR3 IP核的接口信號功能列表如下:

|

信號名 |

位寬 |

I/O |

功能 |

|

clk_in |

1 |

I |

系統的工作時鐘 |

|

rst_n |

1 |

I |

復位信號,低電平有效 |

|

app_rst_n |

1 |

I |

異步復位信號,只對內存設備進行復位,不會重置IP核 |

|

app_init_start |

1 |

I |

IP核初始化開始信號 |

|

app_cmd |

4 |

I |

IP核指令信號 |

|

app_cmd_valid |

1 |

I |

IP核指令有效信號 |

|

app_addr |

28 |

I |

控制器輸出的IP核地址信號 |

|

app_cmd_burst_cnt |

1 |

I |

命令突發計數輸出,指示給定的讀或寫命令被控制器自動重復的次數。控制器還根據命令的突發長度順序生成每個重復命令的地址 |

|

app_ofly_burst_len |

1 |

I |

當前命令及時突發長度 |

|

app_write_data |

64 |

I |

控制器輸出給IP核的外部寫入數據 |

|

app_data_mask |

8 |

I |

用于寫數據的數據掩碼。每個位屏蔽本地寫數據的對應字節 |

|

clocking_good |

1 |

O |

時鐘穩定信號 |

|

burst_finish |

1 |

O |

突發讀/寫操作完成 |

|

app_init_done |

1 |

O |

IP核輸出的初始化完成信號 |

|

app_cmd_rdy |

1 |

O |

命令準備輸出信號,有效時表示內存準備好接收下一個命令和對應的地址,只持續一個時鐘周期 |

|

app_datain_rdy |

1 |

O |

IP核輸出的數據輸入準備完成輸出信號。當它有效時,表示內存已經準備好接收數據 |

|

app_read_data |

64 |

O |

IP核輸入的從DDR3中輸出的數據 |

|

app_read_data_valid |

1 |

O |

讀數據有效輸出信號,當其有效時,表示數據總線上的數據有效讀出 |

|

app_wl_err |

1 |

O |

IP核輸出的寫錯誤指示信號 |

|

app_rt_err |

1 |

O |

IP核輸出的讀錯誤指示信號 |

|

em_ddr_addr |

15 |

O |

內存地址總線,內存的多路復用行和列地址。 |

|

em_ddr_ba |

3 |

O |

內存的bank地址 |

|

em_ddr_cke |

1 |

O |

控制器生成的內存時鐘使能信號 |

|

em_ddr_clk |

1 |

O |

控制器產生的內存時鐘,最高可達到400M |

|

em_ddr_cs_n |

1 |

O |

內存片選 |

|

em_ddr_data |

16 |

I/O |

內存雙向數據總線 |

|

em_ddr_dm |

2 |

O |

DDR3內存寫數據掩碼,為字節級寫屏蔽字節通道 |

|

em_ddr_dqs |

2 |

I/O |

內存雙向數據頻閃 |

|

em_ddr_odt |

1 |

O |

內存終止控制 |

|

em_ddr_cas_n |

1 |

O |

內存列地址頻閃 |

|

em_ddr_ras_n |

1 |

O |

內存行地址頻閃 |

|

em_ddr_reset_n |

1 |

O |

IP核向內存發送的異步復位信號,低電平有效 |

|

em_ddr_we_n |

1 |

O |

內存寫使能 |

四、DDR3 IP核生成過程:

在例化DDR3的IP核之前,需要先生成DDR3的IP核,且DDR3的例化與其他IP核不同,具體的過程如下:

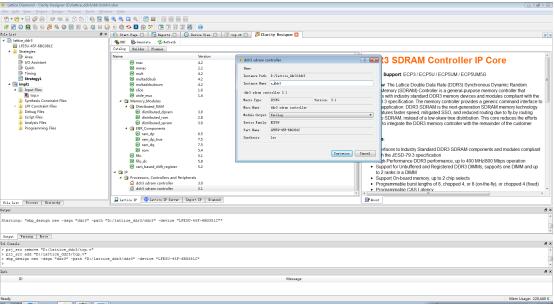

1、首先打開Clarity Designer創建一個IP文件:

2、進入IP核生成界面后,需要在網上下載DDR3的IP核,在Lattice IP Sever中進行聯網下載DDR3的IP核并安裝,安裝完IP核后在Lattice IP中選擇ddr3 sdram controller 3.1,進行IP核參數設計:

3、配置IP核參數,由于選取的器件是ECP5U系列FPGA,因此DDR3的頻率需設置為300M,否則生成的IP核是灰色的無法加入工程中去,內存數據總線大小選擇16,對應的輸入數據位寬是64位,配置選擇X8,對應的地址位寬是28位。

4、IP核生成完成后,點擊系統IP核界面上Generate,會在工程的文件列表中加入一個.sbx文件,此文件就是需要例化的DDR3 IP核實體文件,同時在對應的文件夾下面會出現一個對應名稱的.V文件,將這個.V文件中的信號例化進頂層中即可。

5、需要例化的.V文件:

五、例化IP核

將上圖中的.V文件例化進頂層文件中,定義好信號類型,將對應的信號相連接。至此,DDR3的IP核添加成功。

以上就是lattice DDR3 IP核使用調試的內容分享,加QQ 3358622769 與我進行更深入的討論!