黃同學高速AD項目學習筆記

本文為明德揚原創文章,轉載請注明出處!作者:黃同學

以下是我在做高速AD項目的調試經驗,現在分享出來,希望可以給大家提供一定的幫助。如果發現sync一直沒有同步上,即一直為低,那么就需要檢查同步條件,具體操作如下。

1、檢查是時鐘的正確性

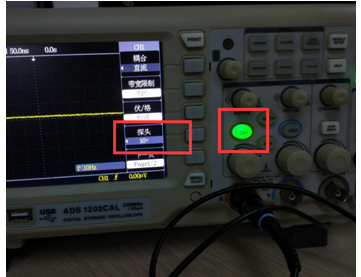

1)需要使用示波器測量時鐘的正確性,示波器設置如下

2)表筆設置,使用前需要自行校準表筆,校準方法這里不再贅述,不會的同學可以在網上搜索方法。

3)測量點

接著對參考時鐘和同步時鐘進行測量,這兩個測量點都是AD9516給AD9144的時鐘,給FPGA的時鐘需要直接測量芯片引腳,比較危險,不建議測。主要測量有無輸出和時鐘頻率是否正確。

AD9516的配置軟件生成的寄存器值不一定正確,部分寄存器的值需要自行修改。之前就遇到過同步時鐘的輸出頻率不對的問題,修改了AD9516的0x19B寄存器的值,問題得到解決。分頻系數=M+N+2,其它寄存器的分頻系數計算方式與此相同。

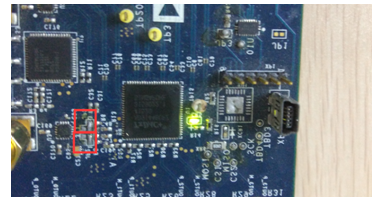

參考時鐘在開發板上的位置如下:

同步時鐘在開發板上的位置如下:

2、AD9144的寄存器正確設置

ACE軟件生成出來的值基本是正確的,但是要注意一下幾點:

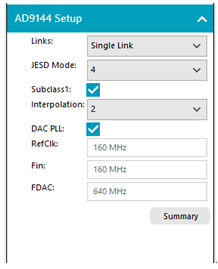

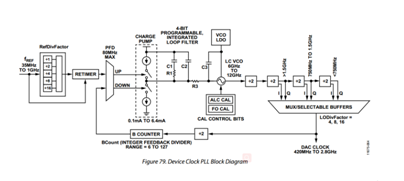

1)正確設置DAC PLL,如下圖所示,其中Ref_clk = 參考時鐘;Fin = 這個時鐘作用不清楚;FDAC = DAC每通道的實際工作頻率,這個值包含插值。

注意:要點應用

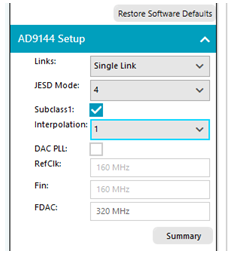

2)正確設置采樣率如下圖所示,

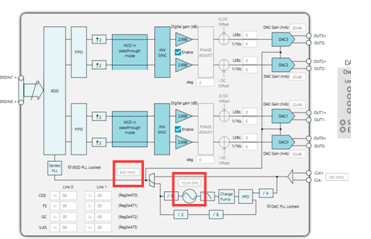

因為乘法器輸出的頻率范圍是6-12GHZ,所以DAC的工作頻率要≥375MHZ,如果不夠,可以通過增加插值的方式來提高頻率,同時也可以不用PLL(此方法未測試)

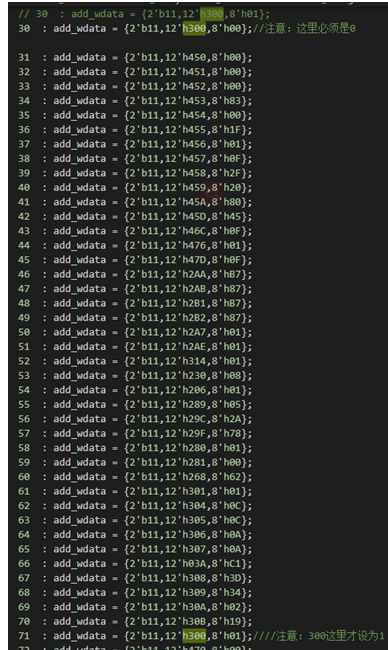

AD9144對寄存器的配置順序有要求,具體順序可以閱讀數據手冊或者看明德揚潘老師的上位機代碼。配置的順序特別注意一個0X300的寄存器,這個寄存器第一次配置要設置為0,第二次配置設置為1

AD9144的要在AD9516配置完成之后等待一段時間才能開始配置,具體等待輸出時鐘穩定的時間可以看AD9516的數據手冊,程序里面的延時是調出來的。AD9144的寄存器的配置速度不能太快,不然也會出現無法同步的現象,具體原因未知,程序里面的延時也是調出來的。

3、IP核設置

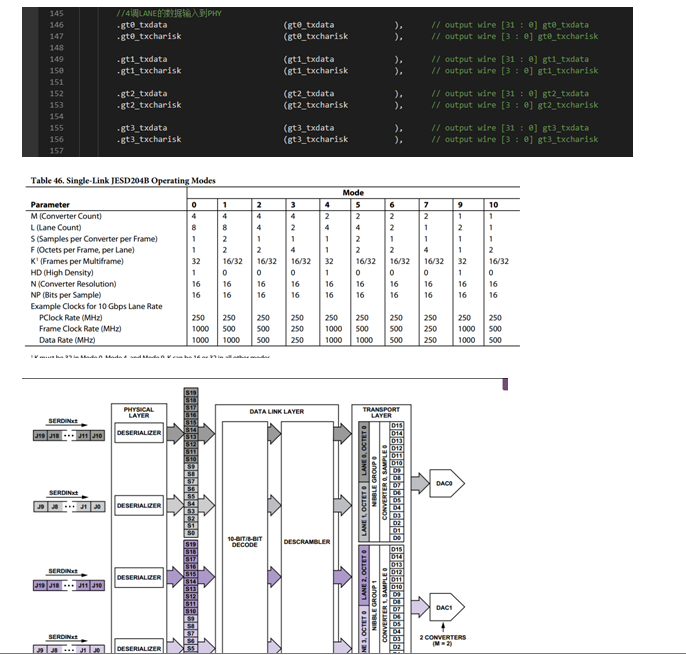

公式計算和IP核設置的F,S,K,Lane,等參數是由選擇的DAC工作模式確定的,其他參數如SCR等,需要怎么設置在AD9144數據手冊里面第50頁(不同版本的數據手冊頁數可能會有偏差)開始有詳細介紹。 IP核是高電平復位的,這里要注意:如果復位住了這幾個會一直等于0,并且無法同步

4、AXI總線配置

具體配置方法參考明德揚潘老師的文檔,經過一次簡單的測試,這個可以不配置也能正常工作,具體沒有詳細測試。

5、時鐘

IP核的tx_core_clk需要PLL產生一個合適的時鐘并且經過BUFG給JESD204B IP核使用;Drp_clk動態調整時鐘我這里沒有用到,但是必須給一個時鐘,并且要和IP核里面設置的頻率相同;AXI時鐘頻率和IP核內設置的相同即可。

6、參數計算

參考明德揚潘老師的文檔,特別注意是要 * 還是 \ 。

舉個例子:20MHZ正弦波,16個點組成一個正弦波,2通道,16bit,插值=2(使用DAC PLL的時候頻率必須≥375MHZ,這例子速率不夠所以要X2)。

1)有效傳輸:20MHZ*16個點*2通道*16bit=10.24Gbit;

2)實際經過8b/10b編碼的速率是:10.24Gbit * 1.25=12.8Gbit這就是4條Lane總共要傳輸的速率;

3)單通道的DAC采樣率(sample_clock):20MHZ*16個點=320MHZ(因為插值=2所以這個值填入ACE的時候要*2=640MHZ,計算的時候依舊使用320MHZ);

4)幀頻率(frame_clock):sample_clock / S=320 / 1 = 320MHZ(S值由DAC模式決定);

5)字符頻率(character_clock):frame_clock*F=320MHZ*1=320MHZ(F值由DAC模式決定);

6)Bit頻率(bit_clock):character_clock*10=320MHZ*10=3.2Gbit;

7)多幀頻率(multi_frame_clock):frame_clock / K=320MHZ / 32 =10MHZ(K由DAC模式決定);

8)同步時鐘(sysref_clock):multi_frame_clock / R =5MHZ(R=2),AD9144數據手冊規定,同步時鐘的最大值是:fdata / (K * S) fdata是哪個沒有細看;

9)設置時鐘(device_clock):multi_frame_clock * D =80MHZ(D取8);

10)Ref_clk:每條Lane的速率/ 40 =3.2Gbit / 40 = 80MHZ;

11)device_clock要≥ref_clk,最好是等于;

12)實際上設置的頻率是160MHZ主要是考慮到插值=2,實際上應該設為80MHZ也能工作(未測試)。

7、實現同步

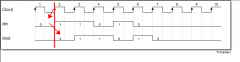

經過上面的設置應該就能同步上了,具體表現為tx_sync信號持續為高電平

8、DAC輸出波形

必須拉高DAC的輸出使能引腳,不然會沒有波形輸出!!!

AD9144是電流型輸出DAC,并且板子上使用變壓器進行放大,所以,不能輸出直流波形只能輸出交變的波形,目前已經測試能輸出正弦波。三角波 和 方波可能無法輸出或者輸出失真。

9、DAC的數據映射

用一個示例展示給大家。

2路DAC輸出 4調lane

波形數據是:

30FB

7640

7FFF

7640

5A81

30FB

0

CF05

A57F

89C0

8001

89C0

A57F

CF05

0

輸入到IP核的數據(tx_tdata)00057fc000cfa58900057fc000cfa589

00 05 7f c0

00 cf a5 89

00 05 7f c0

00 cf a5 89

第2路 DAC(順序得看數據手冊)

00 05 7f c0 lane 3

00 cf a5 89 lane 2

0x0000 0xcf05 0xa57f 0x89c0

第1路 DAC(順序得看數據手冊)

00 05 7f c0 lane 1

00 cf a5 89 lane 0

0x0000 0xcf05 0xa57f 0x89c0

以上就是高速AD項目中實現sync同步的小經驗,不同情況遇到的問題有所不同,希望我的思路可以給大家帶來幫助,同學們也可以在留言評論中與我進行討論。