Xilinx Kintex-7 電源穩(wěn)定性調(diào)試心得(私人總結(jié)版)

本文為明德?lián)P原創(chuàng)文章,轉(zhuǎn)載請注明出處!作者:鄭先生

Xilinx KC705 開發(fā)套件

Xilinx XC7K325T是Kintex-7系列其中一個型號,擁有326K邏輯單元和407K CLB觸發(fā)器,IO資源也達到了500個單端IO,240對差分對。

公司最近在搞的信號采集處理項目就用了這款FPGA,采集模塊部分采用14位、500 MSPS LVDS、雙通道模數(shù)轉(zhuǎn)換器(用的是ADI的AD9684,并行14位LVDS接口,DDR模式)

AD9684

PS:此ADC功能很強大,可說是數(shù)字通信接收機的利器,哈哈,后續(xù)有機會跟大家介紹此ADC的調(diào)試心得。

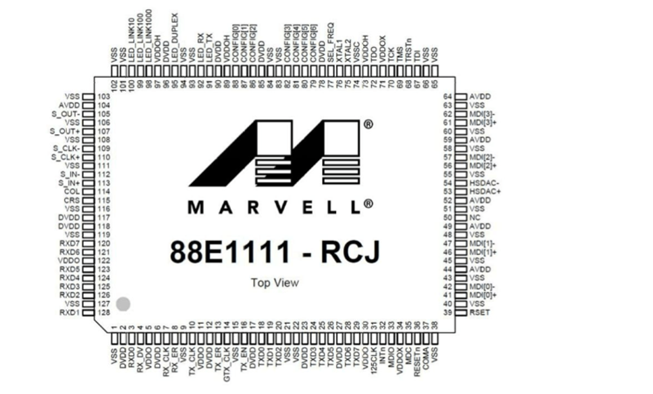

調(diào)試過程很漫長,由于板卡的穩(wěn)定性一直存在問題,FPGA發(fā)熱異常,調(diào)試經(jīng)常遇見莫名其妙的Bug,由于最終采集處理后的數(shù)據(jù)通過千兆以太網(wǎng)發(fā)出,數(shù)據(jù)給予到上位機進行進一步處理,因此千兆以太網(wǎng)PHY芯片采用的是88E1111,它支持RGMII,GMII,SGMII等接口與MAC層連接,相信大家都不會陌生,Marvell 88E1111 PHY芯片價格還是挺高的,但是功能也確實強大。

Marvell 88E1111

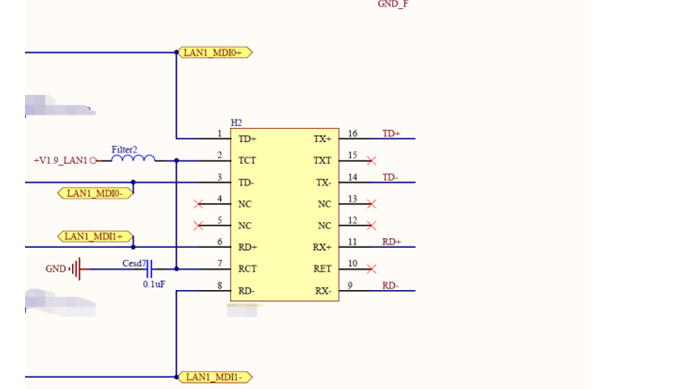

值得一提的是88E1111的MDI線與網(wǎng)口變壓器連接時,中心抽頭需要接VCC,因為88E1111是電流驅(qū)動型IC。

參考接法

至于采用的電源多大,與所用PHY芯片有關(guān),這里不再贅述。 調(diào)試過程中,千兆網(wǎng)口經(jīng)常出現(xiàn)連接斷開的現(xiàn)象,網(wǎng)口變壓器異常發(fā)熱,排查問題時發(fā)現(xiàn)88E1111芯片內(nèi)核電源紋波異常,1.0V的電源,紋波達到了200mV。有意思的是,該電源軌與FPGA 內(nèi)核電源軌,用的VRM是同一個,所以K7的內(nèi)核電源的紋波也達到了200mV左右,也就是誤差達到了±10%,這是不能接受的。至此我們一度懷疑采集處理后數(shù)據(jù)的錯誤是因為該電源的容差過大,導(dǎo)致內(nèi)部邏輯形成保持時間故障。(事實上后續(xù)調(diào)試證實是時序約束問題,這里可以建議大家學(xué)習(xí)一下明德?lián)P的時序約束課程,國內(nèi)少有的)

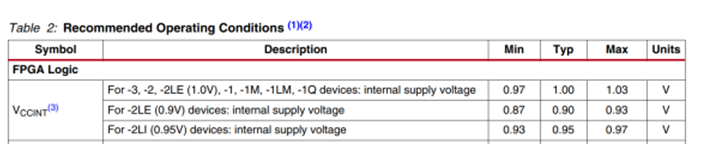

Xilinx 數(shù)據(jù)手冊上指出內(nèi)核電源的為1.0V

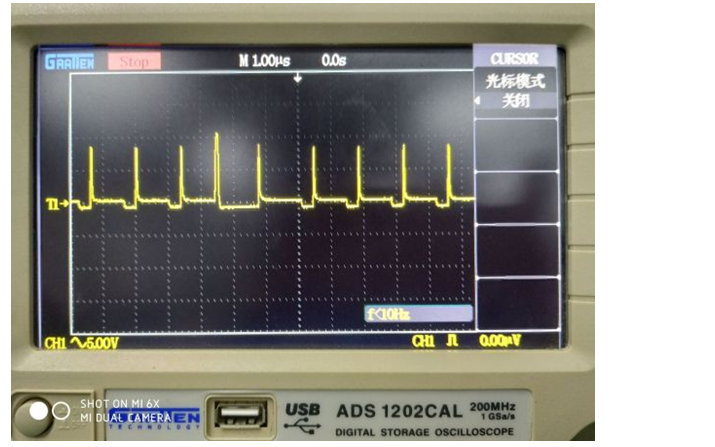

由數(shù)據(jù)手冊可以知道,內(nèi)核電源需要1V±30mV,很顯然該VRM是不滿足要求的。電源IC是來自于TI 的開關(guān)穩(wěn)壓器TPS54620 同步buck 6A輸出,測試時發(fā)現(xiàn)其SW端波形異常,明顯能看出High side 出現(xiàn)突然關(guān)斷,Low side 在High side 關(guān)斷后未導(dǎo)通。

初步判定以為是bootstrap 電路出現(xiàn)問題,認(rèn)為尖峰噪聲導(dǎo)致boot電容擊穿,然而現(xiàn)實是殘酷的,更換boot電容后波形仍然未改變。題主陷入盲目,對補償電路進行試錯法調(diào)試,調(diào)整芯片本振頻率,結(jié)果仍然一樣。無奈之下,靜下心來繼續(xù)研究數(shù)據(jù)手冊

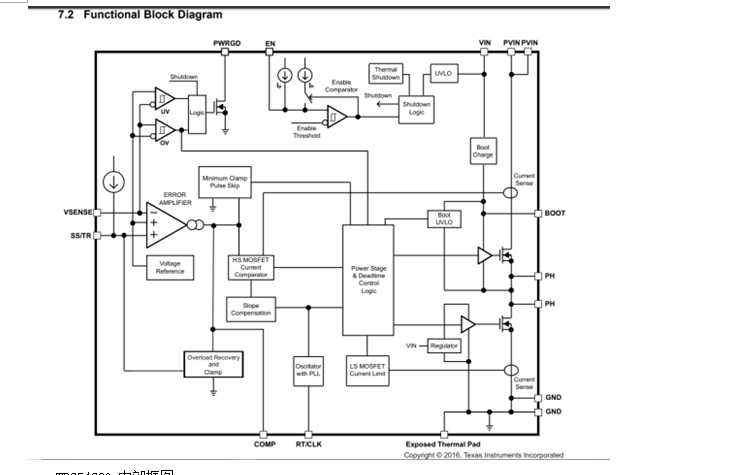

TPS54620 內(nèi)部框圖

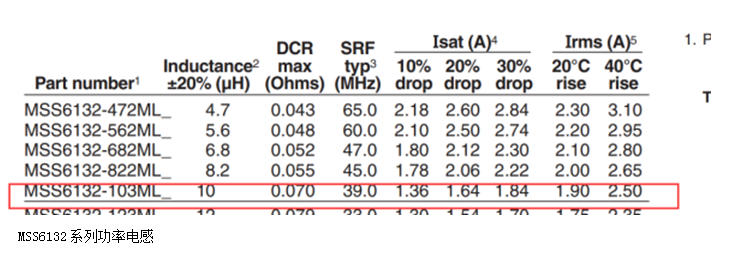

冷靜下來分析了該芯片的內(nèi)部框圖,發(fā)現(xiàn)其High side 與low side 都有電流環(huán)路,認(rèn)為是電流環(huán)路起作用了。但是什么原因?qū)е码娏鳝h(huán)路起作用,此時題主一頭霧水,雖以前設(shè)計過與調(diào)試過低壓大電流的電源模塊,但更多是按照數(shù)據(jù)手冊的指引進行設(shè)計,下載原廠提供的spice模型進行參數(shù)驗證(很多時候照搬參考設(shè)計并不能適合每個板卡,沒有設(shè)備的情況下我都是選擇仿真驗證)。對該VRM的電路參數(shù)進行了一次排查,發(fā)現(xiàn)電感選用的是線藝的MSS6132-103ML_ ,這就存在很大問題了,該電感的飽和電流只有1.6A左右!!

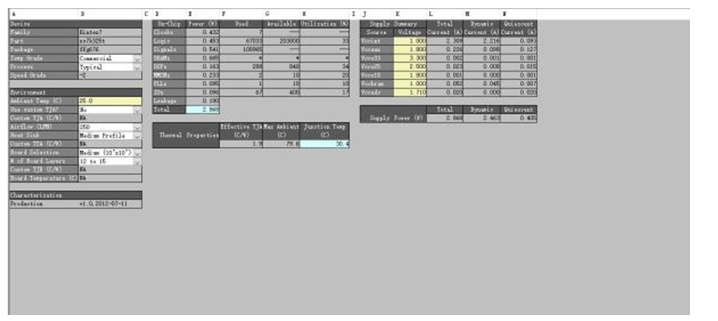

這個電流真的太小了,我認(rèn)為根本帶不動K7的內(nèi)核,更不用說加個88E1111,但是口說無憑,作為技術(shù)人員,感覺可以作為自己的經(jīng)驗方向去調(diào)試,但是憑感覺就下結(jié)論,是萬萬不可為的。所以我打開Xilinx Xpower 功耗分析工具,對已經(jīng)綜合后的工程進行功耗分析,結(jié)果如下

Xpower 界面

分析結(jié)果顯示內(nèi)核電源VCCINT的總電流為2.3A,動態(tài)電流達到了2.2A,大大超過了1.6A。

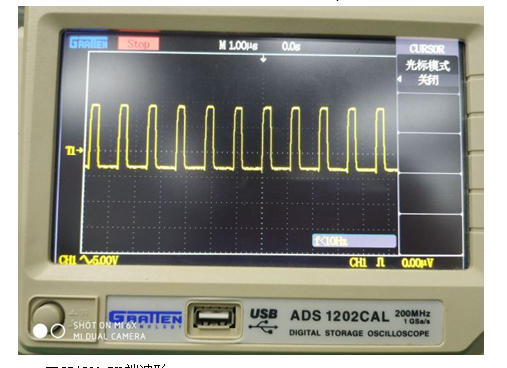

至此,結(jié)論很明顯是電感電流過大達到飽和,失效導(dǎo)致high side直通負(fù)載電流過大,電流環(huán)路起作用關(guān)閉high side 。然后話不多說,直接更換飽和電流更大,感量較低的電感,輸出電容Cout增加一個100uF的MLCC(PS.增加電容的原因是電感改小了,這樣會導(dǎo)致電源功率環(huán)路的LC二階極點左移,在補償電路為改變的前提下,可能會導(dǎo)致電源振蕩),再次測試,SW端波形恢復(fù)正常,紋波也只有幾十mV。

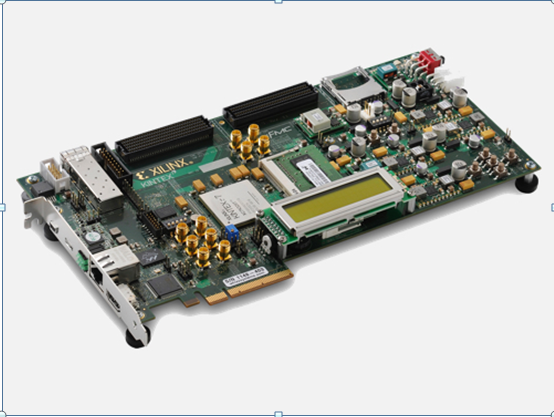

TPS54620 PH端波形

內(nèi)核電源穩(wěn)定后,再次上電調(diào)試,千兆網(wǎng)口通訊正常,FPGA異常發(fā)熱的問題也迎刃而解,我去查了Xilinx官方文獻,內(nèi)核電源不穩(wěn)定是會造成功耗異常。建議使用模塊電源。MPS,ADI,TI等廠商都有專用于7系列FPGA的電源解決方案,體積小,電流大,動態(tài)響應(yīng)快,缺點相對于用PMIC解決方案就是貴。這三家中MPS的模塊電源價格算比較友好了

MPS Kintex-7 模塊電源解決方案

很多工程師都會選擇開關(guān)穩(wěn)壓器作為FPGA板卡的VRM,這樣能省不少成本,但是設(shè)計時應(yīng)該考慮一下VRM的穩(wěn)定性,避免板卡存在隱患,調(diào)試時也能避開許多問題。想要學(xué)習(xí)交流的同學(xué)可以留言給我,也可以聯(lián)系明德?lián)P學(xué)習(xí)更多知識!