SignalTap使用教程

本文為明德揚原創文章,轉載請注明出處!作者:陳刀刀

明德揚設計的工程經常使用到Quartus Ⅱ軟件,其中常用的調試工具就是SignalTap。當代碼經過仿真沒有問題,但加載到FPGA電路板后,發現功能不正確時,我們就可以用signalTap工具進行分析,它的作用就類似于一個數字邏輯分析儀。今天就給大家分享SignalTap的使用教程。

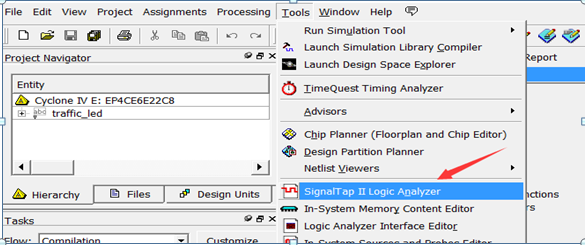

一、打開SignalTap工具

打開Quartus后,在菜單欄中,選擇“Tools”->”SignalTal II Logic Analyzer”,就可以打開SignalTap工具。如下圖:

二,使用SignalTap調試設置步驟

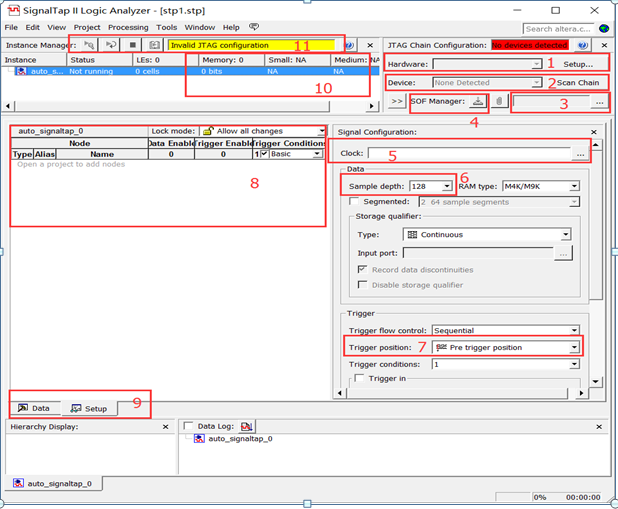

界面示意圖如下所示,其中有對應的標號,其解釋如下:

◆ 1—4為基本的軟硬件配置:1為下載線選擇;2為硬件檢測(識別相關的FPGA設備);3工程配置文件選擇(sof文件);4加載sof文件(1-3均完成后即可加載文件)。

◆ 5為采樣時鐘設置:選擇采樣時鐘,采樣時鐘要根據具體需要進行設置, 可以為模塊的工作時鐘,也可以為內部信號;

◆ 6為采樣深度設置:采樣深度并非越大越好,要根據分析需求進行合理設置;

◆ 7為觸發位置選擇:包括前段觸發、中間觸發、后端觸發三種方式,以觸發點為參考,觸發位置不同,我們能得到不同時間段的信號值。

◆ 8—9為信號設置:包括添加信號,設置信號觸發條件等。在8中空白處雙擊即可添加信號界面,根據需要添加工程中的相應信號,添加信號后即可設置其觸發條件。

◆ 10為資源使用情況指示:如果資源多于FPGA本身的資源,綜合時會報錯,無法進行分析。

◆ 11為運行操作按鈕:開始運行后,待觸發條件滿足后會顯示波形。

三,選擇采樣時鐘

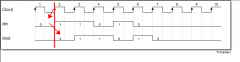

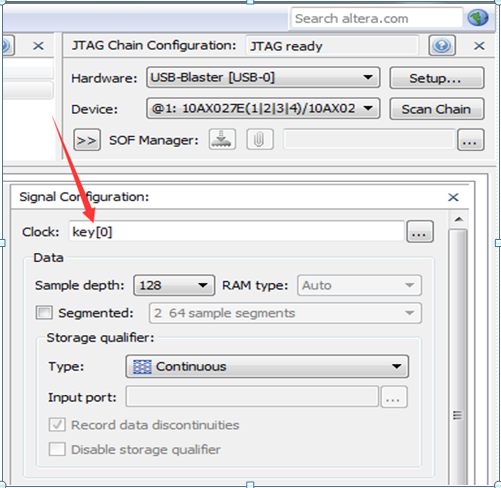

1、SIGNALTAP的采樣時鐘,不一定是時鐘信號,可以是其他任意的信號。總之,SIGNALTAP會在采樣時鐘的上升沿去捕捉信號的值,如果沒有上升沿,則會一直等待。例如下圖所示,就是以按鍵信號key【0】為采樣時鐘。在key【0】由0變1時,就會采樣一個值。

2、若該工程使用到幾個模塊,并且每個模塊的時鐘不一定相同,則我們選擇采樣時鐘時,要根據我們要測試的信號所在的模塊的時鐘是什么。

四,選擇觸發條件的次數

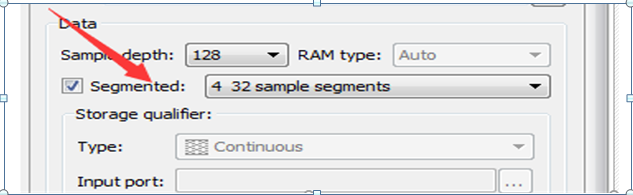

下圖所示,通過設置segmented,可以檢查滿足觸發條件的次數。例如,發現按鍵有時候失靈的情況,為了定位此問題,我想檢查按鍵按下的次數,是否與捕捉到信號次數一致。

其主要設置為:

1. 把segmented設置為32;

2. 把捕捉到信號key_vld拉到顯示窗口,該信號為1表示捕捉到一個按鍵;

3. 設置觸發條件為:key_vld的上升沿;

4. 按下run鍵,等待觸發條件滿足;

5. 按下按鍵4次;

6. 按停止捕捉鍵 。

五,信號的觸發條件

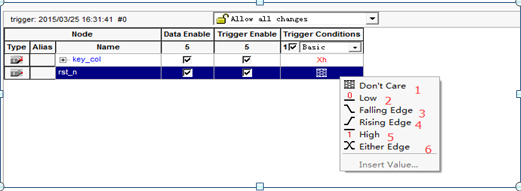

1、如下圖所示,6種觸發條件的含義如下:

don’t care:表示不關心,也即任意,此信號的值不影響觸發條件;

Low :低電平觸發;

Falling Edge:下降沿觸發;

Rising Edge:上升沿觸發;

High:高電平觸發;

Either Edge:雙沿觸發,即有變化時觸發。

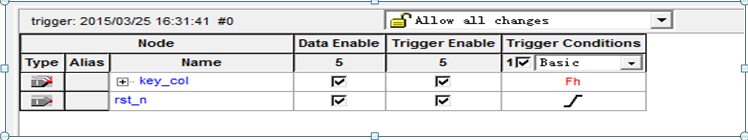

2、假設取上升沿觸發,并對key_col也做觸發條件的設置如下:

此時的觸發條件含義為:當rst_n為上升沿并且key_col全為高時觸發。

注意,這里多觸發條件之間默認的是“與”的關系,很多人會誤認為是“或”的關系。

以上就是SignalTap的使用教程,想要學習更多內容的同學,可以加Q:2777642036陳刀刀 獲取更多關于SignalTap的使用資料!